Xilinx Vivado IDE(Verilog)でFPGA学習ボード「BASYS 3」に簡易デジタル回路を実装

Follow projectこちらの記事について、内容・翻訳・視点・長さなど、皆様のご意見をお送りください。今後の記事製作の参考にしたいと思います。

Thank you! Your feedback has been received.

There was a problem submitting your feedback, please try again later.

こちらの記事の感想をお聞かせください。

この投稿では、Xilinx Vivado IDE で Verilog を使用してデジタル回路を作成し、それを FPGA トレーナーボードに実装するプロセスを説明します。このガイドは、Xilinx University Program (XUP) Vivado Design Flow Lab 1 に基づいて作成されています。

この投稿では、Xilinx Vivado IDE で Verilog を使用してデジタル回路を作成し、それを FPGA トレーナーボードに実装するプロセスを説明します。このガイドは、Xilinx University Program (XUP) Vivado Design Flow Lab 1 に基づいて作成されています。

部品リスト

| Qty | Product | 品番 | |

|---|---|---|---|

| 1 | Digilent 410-183 Basys Artix-7 Development Board | 134-6451 | |

目的

この記事を一通りなぞることで、次のことができるようになります:

- FPGAプログラミング環境「Vivado」上で、Basys3ボード向けにHDLモデルを開発するプロジェクトを作成

- 同梱のXDC(Xilinx Design Constraint)ファイルを使用して、ピンの位置を調整

- Vivado シミュレータを使用してデザインをシミュレーション

- 上記をBasys3ボード上に実装

- ビットストリームを生成します

- 生成されたビットストリームを使用してFPGAを構成し、機能を確認します

手順

ここでは、ステップ毎の一般的概要ステートメントを説明しています。以下の詳細な手順に従って、lab1を進めてください。

デザインの説明

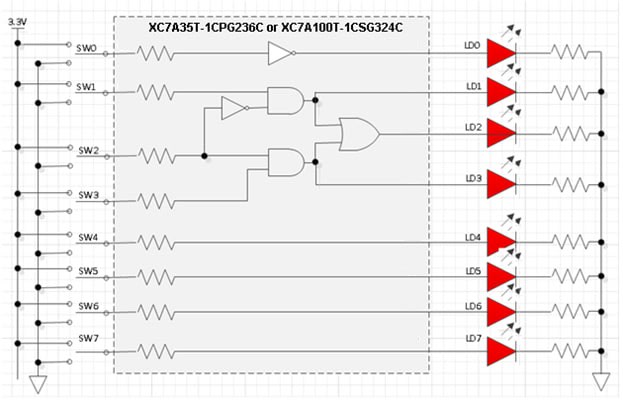

このデザインは、対応する出力LEDに直接接続された複数の入力で構成されています。図1に示すように、入力によっては、その結果がLEDに出力される前に論理的に操作されます。

図1. 完成デザイン図

一般的なフロー

|

ステップ1:IDEを使用してVivadoプロジェクトを作成する |

|

ステップ2:Vivado Simulatorを使用してデザインをシミュレートする |

|

ステップ3:デザインを合成する |

|

ステップ4:デザインを実装する |

|

ステップ5:タイミングシミュレーションを実行する |

|

ステップ6:ハードウェアの機能を確認する |

IDEを使用してVivadoのプロジェクトを作成する(ステップ1)

Vivadoを起動し、vL HDLを使用してXC7A35TCPG236-1(Basys3)をターゲットとするプロジェクトを作成します。

2020_1_artix7_sources\lab1から提供されたlab1.vとlab1.xdcファイルを使用します

[スタート]>[すべてのプログラム]>[Xilinx Design Tools]>[Vivado 2020.1]>[Vivado 2020.1]を選択して、Vivadoを開きます

[Create New Project]をクリックして、ウィザードを開始します。[Create A New Vivado Project]ダイアログボックスが表示されます。[Next]をクリックします。

[New Project]フォームの[Project location]フィールドの[Browse]ボタンをクリックし、C:/Digilent/Basys3Workshop/2020_1_artix7_labsを参照して、[Select]をクリックします。

Project nameにlab1と入力します。[Create Project Subdirectory]ボックスがチェックされていることを確認します。[Next]をクリックします。

図2. Project NameとLocationの入力

[Project Type]で[RTL Project]オプションを選択します。[Do not specify sources at this time]チェックボックスがチェックされていないことを確認してください。[Next]をクリックします。

ドロップダウンボタンを使用して、[Add Sources]でTarget Languageにverilog、Simulator LanguageにMixedを選択します。

図3.Target languageとSimulator languageの選択

[Add Files]ボタンをクリックし、[Downloads folder]を参照して、lab1.vを選択し、[OK]をクリックします。[Copy sources into project]チェックボックスがチェックされていることを確認します。「Next」をクリックして、「Add Constraints」フォームを表示します。

制約ファイルlab1_basys3.xdcとlab1_nexys4.xdcが自動的に追加されます。ウィンドウの右端にある "X "をクリックして、ターゲット・ボード用ではないXDCファイルをハイライトして削除します。[Copy constrains files into project]チェックボックスがチェックされていることを確認します。

ファイルが追加されていない場合は、[Add Files...]ボタンをクリックし、 [Downloads folder] (必要に応じて)を参照して、lab1_basys3.xdcまたはlab1_nexys4.xdcを選択し、[OK](必要に応じて)をクリックして、[Next]をクリックします。

このXilinx Design Constraintsファイルは、FPGA上の物理的なIOロケーションをボード上のスイッチやLEDに割り当てます。この情報は、ボードの回路図またはボードのユーザーガイドのいずれかで得ることができます。

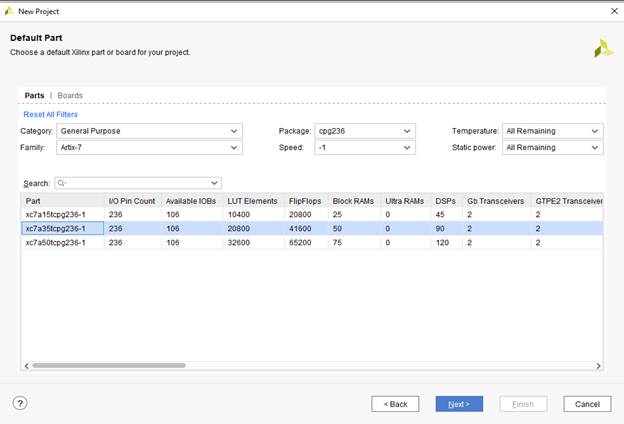

Default Partフォームで、[Parts]オプションと[Filter]の各種ドロップダウンフィールドを使用します。 Basys3ボードを使用する場合は、[XC7A35TCPG236-1]を選択します。[Next]をクリックします。

図4. Basys3の Part Selection

[Boards Specify]オプションを選択し、[Library]フィルターで[Artix-7]を選択して、適切なボードを選択することができます。Nexys4とBasys3は、ツールのデータベースに含まれていないため、リストに表示されていないことに注意してください。

[Finish] をクリックすると、Vivado プロジェクトが作成されます。

Windowsのエクスプローラーを使用して、C:Digilent\Basys3Workshop\2020_1_artix7_labs\lab1ディレクトリを確認します。lab1.cache、lab1.srcs ディレクトリと lab1.xpr(Vivado)プロジェクトファイルが作成されていることが確認できます。lab1.cache ディレクトリは、Vivado プログラムデータベースのプレースホルダーです。lab1.srcsディレクトリの下にconstrs_1とsources_1という2つのディレクトリが作成されその下に;その下にそれぞれコピーされたlab1.xdc(constraint)とlab1.v(source)のファイルが配置されます。

図 5. 生成されたディレクトリ

lab1.design sourceを開き、コンテンツを分析します。

Sourcesペインで、lab1.design sourceエントリをダブルクリックして、ファイルをテキストモードで開きます。

図6.ソースファイルを開く

`timescale 1ns / 1ps

/////////////////////////////////////////////////////////////////////////

// Entity Name: lab1

////////////////////////////////////////////////////////////////////////

module lab1(

input [7:0] swt,

output [7:0] led

);

wire [7:0]intled;

assign intled[0] = !swt[0];

assign intled[1] = swt[1] & !swt[2];

assign intled[3] = swt[2] & swt[3];

assign intled[2] = intled[1] | intled[3];

assign intled[7:4] = swt[7:4];

assign led = intled;

endmodule

VERILOGコードの2-4行目は、エンティティ名とモジュールの目的を記述したコメント行です。

6-9行目では、lab1というmoduleを宣言し、ポートのインターフェース信号を定義しています。入力swt(スイッチ)と出力ledの2つのベクターが使用され、それぞれ8つの信号があります。

10行目は、LEDの状態を作るためのゲートやモジュールを接続するワイヤを宣言しています。

11-15行目では機能を説明し、16行目では計算された値を出力信号に割り当てています。

17行目でモジュールを閉じます。

lab1_basys3.xdcソースを開き、コンテンツを分析します。

[Sources]ペインで[Constraints]フォルダを展開し、[lab1.xdc]entryをダブルクリックして、ファイルをテキストモードで開きます。

図7.constraintファイルを開く

5-20行目では入力スイッチ[7:0]のピン配置を、25-40行目では出力LED[7:0]のピン配置を定義しています。

ソースファイルに対してRTL(レジスタ転送レベル)分析を実行します。

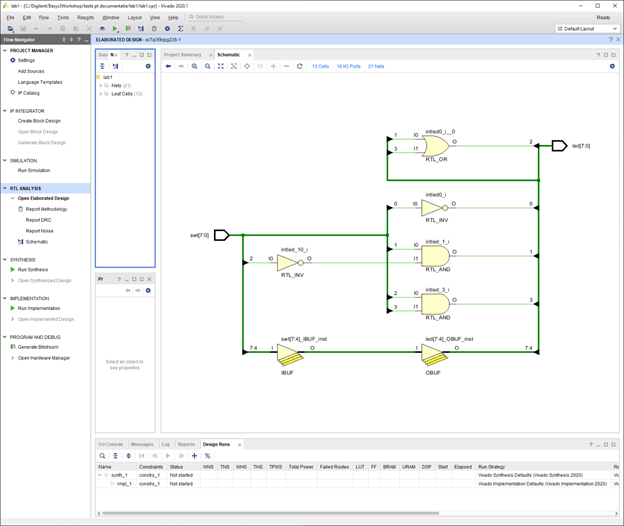

Flow NavigatorペインのRTL AnalysisタスクでOpen Elaborated Designエントリを展開し、[Schematic]をクリックします。

モデル(デザイン)が精緻化され、デザインのロジックビューが表示されます。

図8. デザインのロジックビュー

ファイルでモデル化されているように、スイッチ入力の一部はLEDに出力される前にゲートを通過し、残りはLEDに直接接続されていることに注意してください。

Vivado Simulator Step 2 を使用してデザインをシミュレートする。

lab1_tb.designソース テスト ベンチ ファイルを追加します。

[Flow Navigator]ペインの[Project Manager]タスクの下にある[Add Sources]をクリックします。

図9.ソースの追加

[Add or Create Simulation Sources]オプションを選択し、[Next]をクリックします

図10.シミュレーションソースオプションの選択

[Add Sources Files]フォームで、[Add Files…]ボタンをクリックします。c:\Digilent/Basys3Workshop/2020_1_artix7_sources/lab1フォルダを参照し、lab1_tb.vを選択して、[OK]をクリックします。

[Copy sources into project]のチェックボックスにチェックが入っていることを確認します。[Finish]をクリックします。[Sources]タブを選択し、[Simulation Sources]グループを展開します。lab1_tb.vファイルは[Simulation Sources]グループの下に追加され、lab1.vはその階層にdut(device under test)インスタンスとして自動的に配置されます。

図11.シミュレーションソースの階層

Windowsエクスプローラーを使用して、[sim_1]ディレクトリがlab1.srcsディレクトリのconstrs_1および sources_1ディレクトリと同じレベルに作成されていること、およびlab1_tb.vのコピーが [lab1.srcs > sim_1 > imports > lab1] の下に置かれていることを確認します。[Sources]ペインで[lab1_tb]をダブルクリックして、そのコンテンツを表示します。

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

//Entity Name: lab1_tb

//////////////////////////////////////////////////////////////////////////////////

module lab1_tb();

wire [7:0] leds;

reg [7:0] switches, e_leds;

function [7:0] exp_led;

input [7:0]swt;

begin

exp_led[0] = !swt[0];

// exp_led[0] = swt[0]; // coment the previous line and after uncomment this line

// // this line is use to set a fail in testbench.

// // at the line 33 the output in Tcl console will show the output for

// // led and teh output expected

exp_led[1] = swt[1] & !swt[2];

exp_led[3] = swt[2] & swt[3];

exp_led[2] = exp_led[1] | exp_led[3];

exp_led[7:4] = swt[7:4];

end

endfunction

lab1 DUT(.swt(switches), .led(leds));

integer i;

initial begin

$monitor(leds, switches, e_leds);

for (i=0;i<255;i=i+1)

begin

#50 switches = i[7:0];

#10 e_leds = exp_led(switches);

if (e_leds == leds)

$display("LED output matched at %0t", $time);

else

$display("LED output mis-matched at %0t : expected: %b, actual: %b", $time, e_leds, leds);

end

end

endmodule

図12. セルフチェック・テストベンチ

このモジュールは、テストベンチとしては無効です(テスト用の入出力信号はありません)。

アーキテクチャ宣言は次の通り:

- テストされたコンポーネントDUT(device under test)

- いくつかのwire(ネット型)とreg(レジスタ型)

- 期待値計算のための同じモジュール機能を記述した関数

アーキテクチャーボディは次の通り:

- DUT(device/module under test)をインスタンス化します。

- 刺激の生成を定義し、期待される出力とDUTが提供するものとを比較します。

- シミュレーション実行時に、シミュレータのコンソール・ウィンドウにメッセージを出力します。

Vivadoシミュレータを使用して、デザインを 200 ns でシミュレートします。

[Flow Navigator]ペインの[Project Manager]タスクで[Simulation Settings]を選択します。

[Simulation]プロパティフォームを示す、[Project Settings]フォームが表示されます。

[Simulation]タブを選択し、[Simulation Run Time]の値を200 nsに設定して、[OK]をクリックします。

図13.シミュレーション実行時間の設定

[Flow Navigator]ペインの[Project Manager]タスクの下にある[Run Simulation > Run Behavioral Simulation]をクリックします。

テストベンチおよびソースファイルがコンパイルされ、Vivadoシミュレータが実行されます (エラーがないことを前提としています)。以下に示すようなシミュレータ出力が表示されます。

図14. シミュレータ出力

主として、次のビューが表示されます: (i) [Scopes]、テストベンチの階層やglblのインスタンスが表示されます、(ii) [Objects]トップレベルの信号が表示されます、 (iii) 波形ウィンドウ、そして (iv) [Tcl Console]、シミュレーションの動作が表示されます。なお、使用されるテストベンチはセルフチェックであるため、シミュレーションの実行にしたがって、結果が表示されます。

[lab1.sim]ディレクトリは、いくつかの下位レベルのディレクトリとともに、[lab1]ディレクトリの下に作成されていることに注意してください。

図15. 行動シミュレーション実行後のディレクトリ構造

波形ウィンドウの上部には、下表のように、特定目的に使用できるいくつかのボタンが表示されます。

表1:波形を表示するために使用できるさまざまなボタン

波形全体を見るには、[Zoom Fit]ボタン( )をクリックしてください。

入力が変わると出力も変わることに注意してください。

また、ビューの右上にあるフロートボタンをクリックすると、シミュレーション波形のウィンドウをフロートさせることができます。これにより、シミュレーションの波形を見るためのウィンドウが広くなります。ドック ウィンドウ ボタンをクリックするだけで、フローティングウィンドウをまたGUIに戻すことができます。

図16. フロート ボタン

図17. ドック ウィンドウ ボタン

必要に応じて表示形式を変更します。

波形ウィンドウで[switches[7:0]]を選択し、右クリックして[Radix]を選択、それから[Hexadecimal]を選択します。各出力ビットを見たいので、[leds[7:0]]と[e_led[7:0]]の基数を[binary]にしておきます。

下位レベルの信号をモニターするためにさらに信号を追加し、500nsの間シミュレーションを続けます。

必要に応じて、[Scopes]ウィンドウで[lab1_tb]インスタンスを展開し、そして[dut]インスタンスを選択します。swt[7:0]信号とled[7:0]信号が[Objects]ウィンドウに表示されます。

図18. 下位レベルの信号の選択

下位レベル信号をモニターするには、[swt[7:0]]と[led[7:0]]を選択して波形ウィンドウにドラッグします。

シミュレータツールボタンのリボンバーで、シミュレーションの実行時間フィールドに500 overと入力し、単位フィールドのドロップダウンボタンをクリックして、500 ns(合計700 ns)で実行する場合はns () を選択し、(

) ボタンをクリックします。シミュレーションはさらに500 ns実行されます。

[Zoom Fit]ボタンをクリックして、出力を確認します。

図19.追加の500 nsのシミュレーション実行

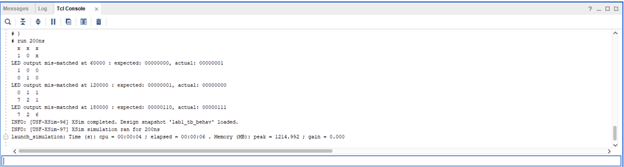

Tclコンソールを観察し、テストベンチがレポートタスクを使用するときに出力が表示されていることを確認します。

図20. 500nsの追加シミュレーションを行った後のTclコンソール出力

[File > Close Simulation]を選択して、シミュレータを閉じます。[OK]をクリックし、それから[No]をクリックして波形を保存せずに閉じます。

13行目をコメントアウトし、12行目をコメントにして、シミュレーションテストに失敗します。

Windows Explorerを使用して、12行目をコメントにして、13行目をコメントアウトします。その後、ファイルを保存し、[Flow Navigator panel]の[Project Manager]タスク下にある[Run Simulation > Run Behavioral Simulation]をクリックします。

図22. 200ns後のシミュレータ出力

使用されるテストベンチはセルフチェックであるため、シミュレーションの実行時に結果が表示されます。Tclコンソールを観察し、テストベンチがレポートタスクを使用して出力が表示されていることを確認します。

図23.Tclコンソールの出力

Tclコンソールでは、信号が不一致の時点で表示されます。たとえば、60nsで、テストベンチは期待される信号(00000000)と実際の信号(00000001)を自動的に表示します。

デザインを合成する(ステップ3)

Vivado 合成ツールでデザインを合成し、Project Summary 出力を分析します。

[Flow Navigator]ペインの[Synthesis]タスク下の[Run Synthesis]をクリックします。

合成プロセスは、lab1.vファイル(およびその階層ファイルが存在する場合はすべて)に対して実行されます。プロセスが完了すると、3つのオプションを含む[Synthesis Completed]ダイアログ ボックスが表示されます。

実装段階に進む前に合成の出力を確認するため、[Open Synthesized Design]オプションを選択し、[OK]をクリックします。

ダイアログボックスが表示された場合、[Yes]をクリックして、詳細デザインを閉じます。

[Project Summary]タブを選択し、さまざまなウィンドウを理解します。

Project Summaryタブが表示されない場合は、[Layout > Default Layout]を選択するか、[Project Summary]アイコンをクリックしてください。

図21. Project Summary ビュー

様々なリンクをクリックして、どのような情報が得られるのか、また、どのリンクをクリックすれば合成設定を変更できるのかを確認してください。

[Project Summary]タブの[Table]タブをクリックします。

使用される推定3つのLUTと16のIO(8つの入力と8つの出力)があることが分かります。

図22. Basys3のリソース使用率推定の概要

[Synthesis](必要に応じて[Synthesized Design]を展開)下の[Flow Navigator]で、[Schematic]をクリックすると、合成されたデザインが回路図ビューで表示されます。

図23. 合成されたデザインの回路図

入力と出力がバッファリングされると、IBUFとOBUFが自動的にデザインにインスタンス化(追加)されることに注意してください。論理ゲートはLUTに実装されています(1入力はLUT1、2入力はLUT2、3入力はLUT3と表記)。RTL分析出力の4つのゲートは、合成出力の4つのLUTにマッピングされます。

Windows Explorerを使用して、[lab1] の下に[lab1.rans]ディレクトリが作成されていることを確認します。[runs]ディレクトリの下に、合成に関連するいくつかのファイルを保持する[synth_1]ディレクトリが作成されます。

図24.デザイン合成後のディレクトリ構造

デザインを実装する(ステップ4)

[Vivado Implementation Defaults(Vivado Implementation 2020)]設定を使用してデザインを実装し、[Project Summary]の出力を分析します。

[Flow Navigator]ペインの[Implementation]タスク下の[Run Implementation]をクリックします。

実装プロセスは、合成デザインで実行されます。プロセスが完了すると、3つのオプションを含む[Implementation Completed]ダイアログ ボックスが表示されます。

デバイスビュータブで実装されたデザインを確認するため、[Open implemented design]を選択し、[OK]をクリックします。

プロンプトが表示されたら、[Yes]をクリックして、合成されたデザインを閉じます。

実装されたデザインが開かれます。

[Netlist]ペインで、ネットの1つ(led_OBUF [1]など)を選択し、ネットがデバイスビュータブのX1Y1クロック領域に表示されていることを確認します(表示するにはズームインする必要がある場合があります)。

選択されていない場合は、[Routing Resources]アイコンをクリックして、ルーティングリソースを表示します。

図25.ネットの選択

図26. Basys3に実装されたデザインを見る

実装されたデザインビューを閉じ、[Project Summary]タブを選択して(デフォルトのレイアウトビューに変更する必要がある場合があります)、結果を確認します。

[Post-Implementation]タブを選択します。

実際のリソース使用率は3つのLUTと16のIOのものであることに注意してください。また、このデザインにはタイミング制約が定義されていないことを示しています(デザインがコンビナトリアルであるため)。

図27. Basys3の実装結果

Windows Explorerを使用して、[impl_1]ディレクトリが[lab1.runs]ディレクトリの下の[synth_1]と同じレベルに作成されていることを確認します。[impl_1]ディレクトリには、実装レポートファイルを含むいくつかのファイルが含まれています。

Vivadoで、下部パネルの[Reports]タブを選択し(表示されていない場合は、メニューバーの[Window]をクリックして[Reports]を選択します)、[Place Design]セクション下の[Utilization Report]エントリをダブルクリックします。レポートは、リソース使用率を示す補助ビューペインに表示されます。なお、コンビナトリアルデザインのため、レジスタは使用していません。

図28.表示可能なレポート

タイミングシミュレーションを実行する (ステップ5)

タイミングシミュレーションを実行します。

[Flow Navigator]ペインの[Simulation]タスク下の、[Run Simulation > Run Post-Implementation Timing Simulation]プロセスを選択します。

実装されたデザインと[lab1_tb]をトップレベルモジュールとして使用して、Vivadoシミュレータを起動します。

Windows Explorerを使用して、[timing]ディレクトリが[lab1.sim > sim_1 > impl]ディレクトリの下に作成されていることを確認します。[timing]ディレクトリには、タイミングシミュレーションを実行するために生成されたファイルが含まれています。

[Zoom Fit]ボタンをクリックして、0-200 nsの波形ウィンドウを表示します。

50 ns(スイッチ入力が0000000bに設定されている箇所)で右クリックし、[Markers > Add Marker]を選択します。

同様に、[leds]が変化する55.000 ns付近で右クリックしてマーカーを追加します。

Add Markerボタン( )をクリックして、マーカーを追加することもできます。[Add Marker]ボタンをクリックし、[e_led]が変化する60 ns付近で左クリックします。

図29.タイミングシミュレーションの出力

入力が変更されてから10 ns後に期待されるLEDの出力をモニターした(テストベンチを参照)のに対し、実際の遅延は約5.000 nsであることに注意してください。

変更を一切保存せずに、[File > Close Simulation]を選択して、シミュレータを閉じます。

ビットストリームを生成して機能を確認する(ステップ6)

ボードを接続して電源を入れます。ビットストリームを生成し、ハードウェアセッションを開き、FPGAをプログラムします。

Micro-USBケーブルがJTAG PROGコネクタ(電源コネクタの隣)に接続されていることを確認します。

ボードがUSB電源を使用するように設定されていることを確認します(Basys3のPower SelectジャンパーJP2を介して)。

図30. Basys3のボード接続

ボードの電源を[ON]にします。

[Flow Navigator]ペインの[Program and Debug]タスクの下にある[Generate Bitstream]エントリをクリックします。

ビットストリーム生成プロセスは、実装されたデザインで実行されます。プロセスが完了すると、2つのオプションを含む[Bitstream Generation Completed]ダイアログボックスが表示されます。

図31.ビットストリームの生成

このプロセスにより、[lab1.runs]ディレクトリ内の[impl_1]ディレクトリ下に、[lab1.bit]ファイルが生成されます。

[Open Hardware Manager]オプションを選択し、[OK]をクリックします。

ハードウェア・マネージャー・ウィンドウが開き、「未接続」の状態が表示されます。

[Open target]のリンクをクリックします。

図32.新しいハードウェアターゲットを開く

[Auto Connect]をクリックし、Vivadoが検出して接続するのを待ちます。

ハードウェアセッションのステータスが[未接続]からサーバー名に変わり、デバイスがハイライト表示されます。また、「ステータス」が「プログラムされていない」ことを示していることに注意してください。

図33.Basys3用に開いたハードウェアセッション

緑色の情報バーの[Program]リンクをクリックして、ターゲットFPGAデバイスをプログラムします。

もう1つの方法は、デバイスを右クリックして[Program Device] ...を選択することです。

図34.FPGAをプログラムするための選択

[Program]をクリックすると、FPGAをプログラムすることができます。

デバイスのプログラムが完了するとDONEランプが点灯します。スイッチの位置によっては、他のLEDが点灯する場合があります。

スイッチを切り替えて、LEDの出力を観察して、機能を確認します(先ほどのロジック図を参照)。

問題がなければ、ボードの電源を[OFF]にします。

[File > Close Hardware Manager]を選択して、ハードウェアセッションを閉じます。

[OK]をクリックしてセッションを閉じます。

[File > Exit]を選択して[Vivado]プログラムを終了し、[OK]をクリックします。

結論

Vivadoソフトウェアツールを使用して、完全なデザインフローを実行することができます。プロジェクトは、提供されたソースファイル(HDLモデルとユーザー制約ファイル)を使用して作成されました。モデルの機能を検証するために、提供されているテストベンチを使った動作シミュレーションが実行されました。次に、モデルが合成、実装され、ビットストリームが生成されました。タイミングシミュレーションは、同じテストベンチを使用して、実装されたデザインで実行されました。機能は、生成されたビットストリームを使用してハードウェアで検証されました。

コメント