FPGA開発ボードとザイリンクス Vivado IDE (VHDL)で 単純なデジタル回路を構築してみる

Follow projectQue pensez-vous de cet article ? Aidez-nous à vous fournir un meilleur contenu.

Merci! Vos commentaires ont été reçus.

There was a problem submitting your feedback, please try again later.

Que pensez-vous de cet article ?

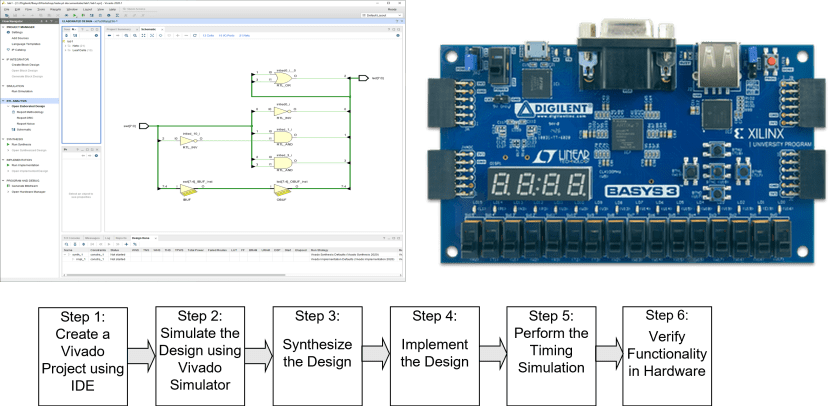

このチュートリアルでは、Xilinx製Vivado IDE で VHDL を使用してデジタル回路を作成し、それを FPGA開発ボードに書き込み実装するプロセスについて説明します。 このガイドは、Xilinx University Program (XUP) Vivado Design Flow Lab 1 に基づいて作成されています。

このチュートリアルでは、Xilinx製Vivado IDE で VHDL を使用してデジタル回路を作成し、それを FPGA開発ボードに書き込み実装するプロセスについて説明します。 このガイドは、Xilinx University Program (XUP) Vivado Design Flow Lab 1 に基づいて作成されています。

Parts list

| Qty | Produit | Part number | |

|---|---|---|---|

| 1 | Digilent 410-183 Basys Artix-7 Development Board | 134-6451 | |

目的

この手順によって、次のことができるようになります:

- HDLモデルをソースとし、Basys 3 FPGA開発ボード上のFPGAチップ用のVivadoプロジェクトを作成

- 提供されているザイリンクス デザイン制約 (XDC) ファイルを使用して、ピン位置を制約

- Vivado シミュレータでシミュレーション

- デザインの合成と実装

- ビットストリームを生成

- 生成されたビットストリームを使用して FPGA を構成し機能を検証。

手順

このチュートリアルは、以下の詳細な手順に関する情報を提供する一般的な概要ステートメントで構成されるステップに分かれています。 これらの詳細な手順に従って、lab1 を進めてください。

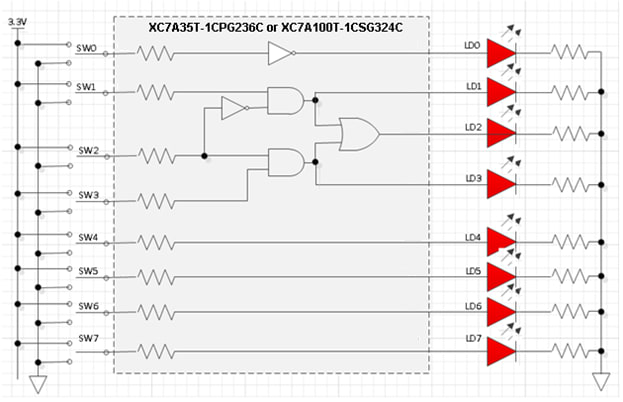

回路の説明

今回作成する回路は、LEDに繋がったいくつかの出力と入力で構成されています。 図 1 に示すように、残りの LED に結果が出力される前に、他の入力が論理的に処理されます。

図 1. 作成する回路

一般的な流れ

|

手順 1: IDE を使用して Vivado プロジェクトを作成 |

|

手順 2: Vivado シミュレータを使用してデザインをシミュレーション |

|

手順 3: 回路のの合成 |

|

手順 4: 回路を実装 |

|

手順 5: タイミング シミュレーションの実行 |

|

手順 6: ハードウェアの機能を確認 |

IDE を使用して Vivado プロジェクトを作成 (手順 1)

Vivado を起動し、XC7A35TCPG236-1 (Basys3) をターゲットとし、VHDL HDL を使用するプロジェクトを作成します。 2020_1_artix7_sources\lab1 から提供された lab1.vhd および lab1.xdc ファイルを使用します。

Startを選択して Vivado を開きます> All Programs > Xilinx Design Tools > Vivado 2020.1> Vivado 2020.1

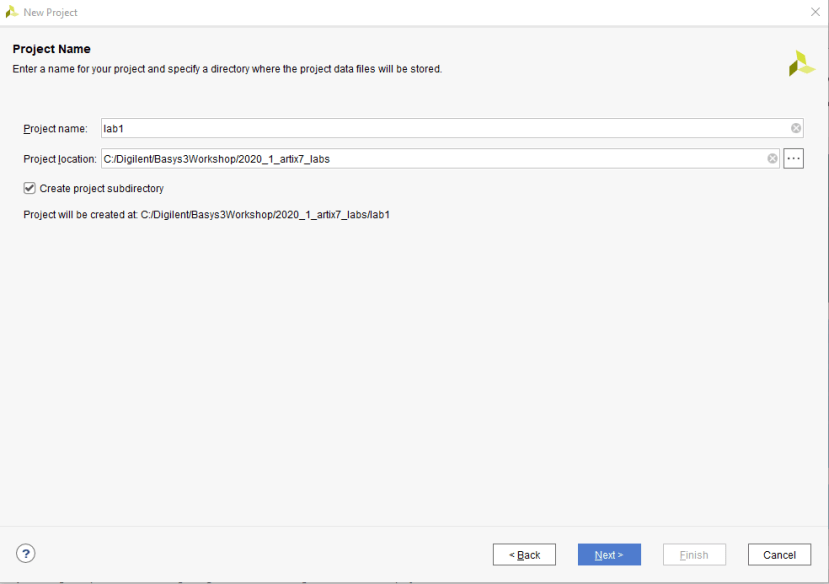

[Create New Project ] をクリックしてウィザードを開始すると、[Create A New Vivado Project ] ダイアログ ボックスが表示されます。Nextをクリックします。

New Project フォームの Project location フィールドの Browse ボタンをクリックし、C:/Digilent/Basys3Workshop/2020_1_artix7_labsを参照して、Select をクリックします。

「Project name」に「lab1」と入力し、「Create Project Subdirectory 」ボックスがチェックされていることを確認して、「Next」をクリックします。

図 2. プロジェクト名と場所のエントリ

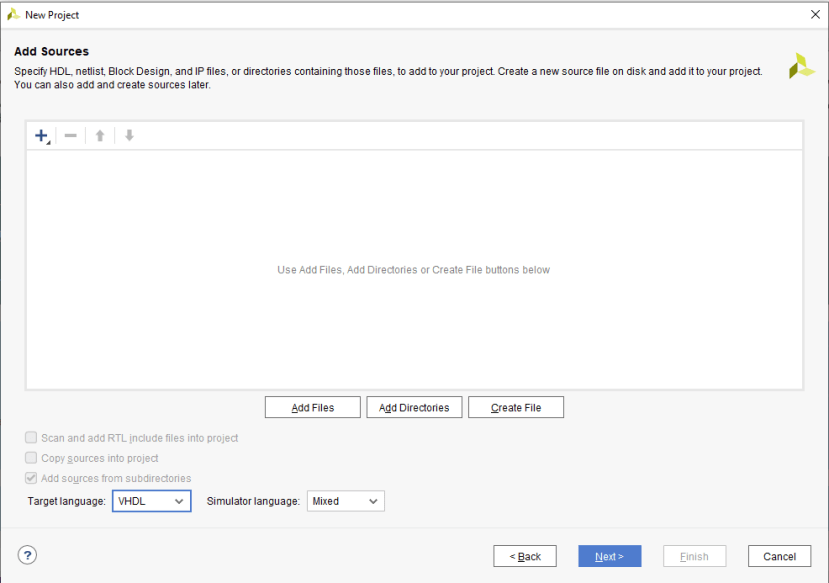

Project Type で RTL Project オプションを選択します。Do not specify sources at this time ボックスがオフになっていることを確認してください。[Next] をクリックします。

ドロップダウン ボタンを使用して、[Target Language ] として VHDL を選択し、[Add Sources] で [Mixed Simulator Language ] を選択します。

図 3. ターゲット言語とシミュレーター言語の選択

Add Files ボタンをクリックし、Downloads folderを参照して、lab1.vhdを選択し、OKをクリックします。Copy sources into project ボックスがオンになっていることを確認します。Nextをクリックします。Add Constraints フォームに移動します。

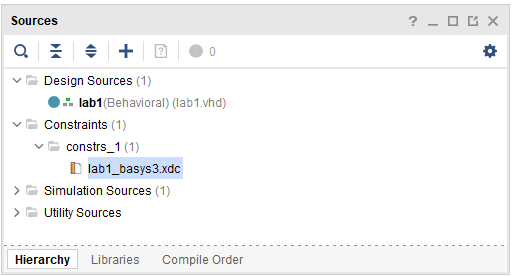

制約ファイル lab1_basys3.xdc および lab1_nexys4.xdc が自動的に追加されます. ウィンドウの右側にある [X] をクリックして、ターゲット ボード用ではない XDC ファイルを強調表示して削除します。Copy constrains files into project ボックスがオンになっていることを確認します。

ファイルが追加されていない場合は、[Add Files… ...] ボタンをクリックし、[Downloads folder ] を参照して (必要な場合)、lab1_basys3.xdc または lab1_nexys4.xdc を選択し、[OK] をクリックします (必要な場合)。 [Next] をクリックします。

このザイリンクス デザイン制約ファイルは、FPGA 上の物理 IO ロケーションをボード上のスイッチおよび LED に割り当てます。 この情報は、ボードの回路図またはボードのユーザー ガイドから入手できます。

[Default Part ] フォームで、[Parts] オプションと [Filter] のさまざまなドロップダウン フィールドを使用します Basys3 ボードを使用している場合は、XC7A35TCPG236-1 を選択し、[Next] をクリックします。

図 4. Basys3 の部品選択

Boards Specify オプションを選択し、Library フィルターで Artix-7 を選択して、適切なボードを選択できます。Nexys4 と Basys3 はツール データベースにないため、リストされていないことに注意してください。

[Finish] をクリックして Vivado プロジェクトを作成します。

Windows Explorer を使用して C:\Digilent\Basys3Workshop\2020_1_artix7_labs\lab1 ディレクトリを確認すると、lab1.cache および lab1.srcs ディレクトリと lab1.xpr (Vivado) プロジェクト ファイルが作成されていることがわかります。ディレクトリは Vivado プログラム データベースのプレースホルダーです.2 つのディレクトリ constrs_1 と sources_1 が lab1.srcs ディレクトリの下に作成され、その下にコピーされた lab1.xdc (制約) と lab1.v (ソース) ファイルがそれぞれ配置されます。

図 5. 生成されたディレクトリ

lab1.vhd ソースを開き、内容を分析します。

[Sources ] ペインで、lab1.vhd エントリをダブルクリックしてファイルをテキスト モードで開きます。

図 6. ソース ファイルを開く

VHDL コードでは、行 1 ~ 3 はエンティティ名とモジュールの目的を説明するコメント行で、行 5 ~ 6 は標準の IEEE ライブラリと STD_LOGIC_1164 パッケージを呼び出します。

行 8 ~ 11 は、lab1 というエンティティを宣言し、ポート インターフェイス信号を定義します. 2 つの std_logic ベクトルが使用され、それぞれ 8 つの信号: 入力 swt (スイッチ) と出力 led.

13 行目では、lab1 エンティティの Behavioral というアーキテクチャを宣言しています。15 行目では、LED の状態を構築するための内部信号を宣言しています。

行 19 ~ 24 は機能を記述し、行 26 は計算された値を出力信号 led に割り当てます。

28 行目でアーキテクチャを閉じます。

lab1_basys3.xdc または lab1_nexys4.xdc ソースを開き、内容を分析します。

[Sources] ペインで、[Constraints] フォルダーを展開し、lab1.xdc エントリをダブルクリックしてファイルをテキスト モードで開きます。

図 7. 制約ファイルを開く

行 5 ~ 20 は入力スイッチ [7:0] のピン位置を定義し、行 25 ~ 40 は出力 LED [7:0] のピン位置を定義します。

ソース ファイルに対して RTL (レジスタ転送レベル) 解析を実行します。

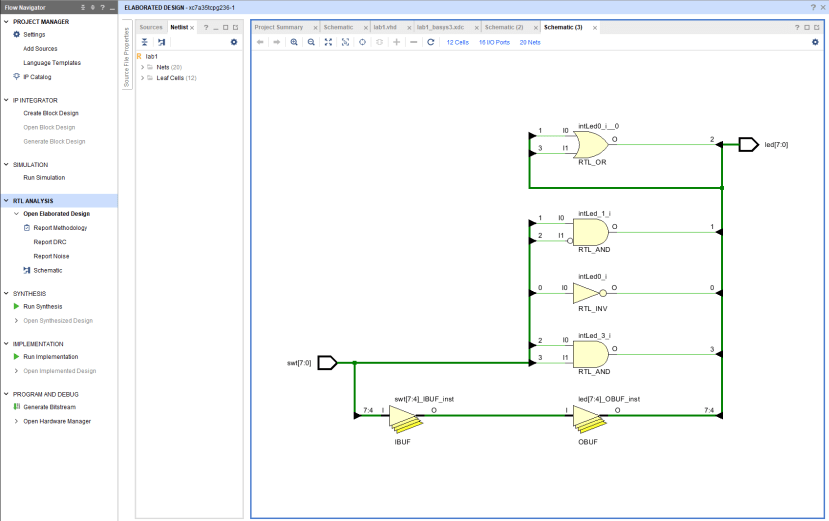

[Flow Navigator ] ペインの [RTL Analysis ] タスクの下にある [Open Elaborated Design] エントリを展開し、[Schematic] をクリックします。

モデル (デザイン) がエラボレートされ、デザインのロジック ビューが表示されます。

図 8. 設計のロジック ビュー

スイッチ入力の一部は LED に出力される前にゲートを通過し、残りはファイルでモデル化されているように直接 LED に送られることに注意してください。

Vivado シミュレータを使用したデザインのシミュレーション 手順 2

lab1_tb.vhd テストベンチ ファイルを追加します。

Flow Navigator ペインの Project Manager タスクの下にある Add Sources をクリックします。

図 9. ソースの追加

[Add or Create Simulation Sources ] オプションを選択し、[Next] をクリックします。

図 10. シミュレーション ソース オプションの選択

[Add Sources Files ] フォームで、[Add Files… ] ボタンをクリックし、c:\Digilent/Basys3Workshop/2020_1_artix7_sources/lab1 フォルダーを参照して、lab1_tb.vhd を選択し、[OK] をクリックします。

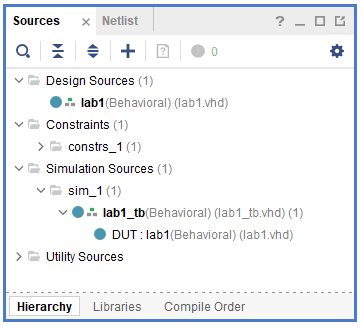

[Copy sources into project ] ボックスがオンになっていることを確認します。[Finish] をクリックします。[Sources] タブを選択し、[Simulation Sources ] グループを展開します。lab1_tb.vhd ファイルが [Simulation Sources ] グループに追加され、lab1.vhd が自動的に配置されます。 dut (テスト対象のデバイス) インスタンスとしてその階層で。

図 11. シミュレーション ソースの階層

Windows Explorer を使用して、sim_1ディレクトリが lab1.srcs ディレクトリの下の constrs_1 および sources_1 ディレクトリと同じレベルに作成されていること、および lab1_tb.vhd のコピーが lab1.srcs > sim_1 > imports > lab1.Double の下に配置されていることを確認します。 [ソース] ペインで lab1_tb をクリックして、その内容を表示します。

----------------------------------------------------------------------------------

-- Entity Name: lab1_tb

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

entity lab1_tb is

end lab1_tb;

architecture Behavioral of lab1_tb is

-- component declaration for the Unit Under Test (UUT)

COMPONENT lab1 is

Port (swt : in STD_LOGIC_VECTOR (7 downto 0);

led : out STD_LOGIC_VECTOR (7 downto 0));

end COMPONENT;

signal switches, leds, e_leds: std_logic_vector(7 downto 0);

function expected_led (swt : std_logic_vector(7 downto 0))

return std_logic_vector is

variable exp_led: STD_LOGIC_VECTOR (7 downto 0);

begin

exp_led(0) := not swt(0);

-- exp_led(0) := swt(0); -- replace the previous line with this one, to fail the test

exp_led(1) := swt(1) and not swt(2);

exp_led(3) := swt(2) and swt(3);

exp_led(2) := exp_led(1) or exp_led(3);

exp_led(7 downto 4) := swt(7 downto 4);

return exp_led;

end expected_led;

begin

DUT: lab1

port map(

swt => switches,

led => leds);

test: process

begin

for i in 0 to 255 loop

wait for 50ns;

switches <= conv_std_logic_vector(i,8);

wait for 10ns;

e_leds <= expected_led(switches);

wait for 0ns;

if leds = e_leds then

report "LED output matched at " & time'IMAGE(now);

else

report "LED output mis-matched at " & time'IMAGE(now) & ": expected: "

& std_logic'Image(e_leds(7)) & std_logic'Image(e_leds(6)) & std_logic'Image(e_leds(5))

& std_logic'Image(e_leds(4)) & std_logic'Image(e_leds(3)) & std_logic'Image(e_leds(2))

& std_logic'Image(e_leds(1)) & std_logic'Image(e_leds(0)) & " actual: "

& std_logic'image(leds(7)) & std_logic'image(leds(6)) & std_logic'image(leds(5))

& std_logic'image(leds(4)) & std_logic'image(leds(3)) & std_logic'image(leds(2))

& std_logic'image(leds(1)) & std_logic'image(leds(0));

end if;

end loop;

end process;

end Behavioral;

図 12. セルフチェック テストベンチ

テストベンチは IEEE ライブラリと必要なパッケージを呼び出します. conv_std_logic_vector 関数を使用するには IEEE.STD_LOGIC_ARITH パッケージが必要です.

エンティティはテストベンチでは無効です (テストの入力信号または出力信号はありません)。

アーキテクチャ宣言は:

- 被試験コンポーネント DUT (被試験デバイス)

- いくつかのシグナル

- 期待値計算用の同じモジュール機能を記述する関数

アーキテクチャ本体:

- DUT (被試験デバイス/モジュール) をインスタンス化します。。

- 刺激の生成を定義し、期待される出力を DUT が提供するものと比較します。

- シミュレーションの実行時に、シミュレータ コンソール ウィンドウにメッセージを出力します。

Vivado シミュレータを使用して 200 ns のデザインをシミュレートします。

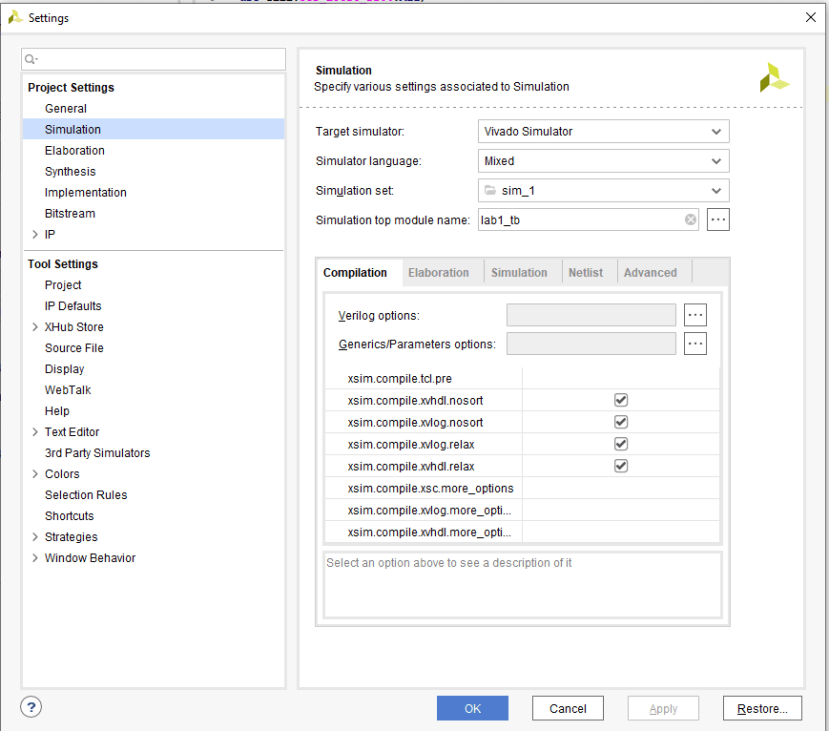

Flow Navigator ペインのProject Manager タスクの下にある [Simulation Settings ] を選択します。

「Project Settings 」フォームが表示され、「Simulation」プロパティ フォームが表示されます。

[Simulation] タブを選択し、[Simulation Run Time ] の値を 200 ns に設定して [OK] をクリックします。

図 13. シミュレーション実行時間の設定

Flow Navigator ペインの Project Manager タスクの下にある Run Simulation > Run Behavioral Simulationをクリックします。

テストベンチとソース ファイルがコンパイルされ、Vivado シミュレータが実行されます (エラーがない場合)。次のようなシミュレータ出力が表示されます。

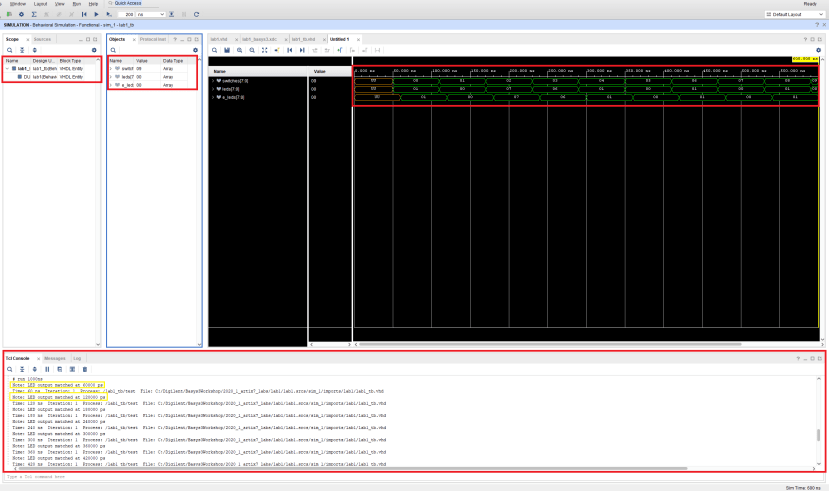

図 14. シミュレーターの出力

4 つの主要なビューが表示されます: (i) Scopes, テストベンチ階層と glbl インスタンスが表示される場所, (ii) Objects, トップレベルの信号が表示される場所, (iii) 波形ウィンドウ, と (iv) Tcl Console シミュレーション アクティビティが表示される場所. 使用されているテストベンチはセルフチェックであるため、シミュレーションを実行すると結果が表示されることに注意してください。

lab1.sim ディレクトリが lab1 ディレクトリの下に作成され、いくつかの下位レベルのディレクトリがあることに注意してください。

図 15. ビヘイビア シミュレーション実行後のディレクトリ構造

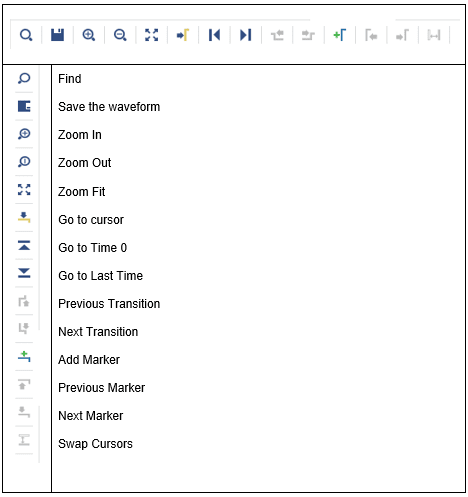

波形ウィンドウの上にいくつかのボタンが表示されます。これらのボタンは、下の表にリストされている特定の目的に使用できます。

表 1: 波形を表示するために使用できるさまざまなボタン

Zoom Fit ボタン ( ) をクリックして、波形全体を表示します。

入力が変化すると出力が変化することに注意してください。

ビューの右上にある [フロート] ボタンをクリックして、シミュレーション波形ウィンドウをフロートすることもできます. これにより、シミュレーション波形を表示するウィンドウが広くなります. フローティング ウィンドウを GUI に再統合するには、 Dock Window ボタンをクリックするだけです。

図 16. フロート ボタン

図 17. Dock ウィンドウ ボタン

必要に応じて表示形式を変更します。

波形ウィンドウで switches[7:0] を選択し、右クリックして [基数] を選択し、次に [16 進数] を選択します。必要に応じて、leds[7:0] と e_led[7:0] 基数をバイナリのままにします。各出力ビットを参照してください。

さらに信号を追加して下位レベルの信号を監視し、シミュレーションを 500 ns 実行し続けます。

必要に応じて、「Scopes」ウィンドウで lab1_tb インスタンスを展開し、dut インスタンスを選択します。swt[7:0] および led[7:0] 信号が「Objects」ウィンドウに表示されます。

図 18. 低レベル信号の選択

swt[7:0] と led[7:0] を選択して波形ウィンドウにドラッグし、これらの低レベル信号を監視します。

シミュレーター ツール ボタンのリボン バーで、シミュレーション ランタイム フィールドに 500 over と入力し、単位フィールドのドロップダウン ボタンをクリックして ns () 500 ns (合計 700 ns) 実行する場合は、(

) ボタン. シミュレーションはさらに 500 ns 実行されます。

「Zoom Fit 」ボタンをクリックして、出力を観察します。

図 19. さらに 500 ns シミュレーションを実行

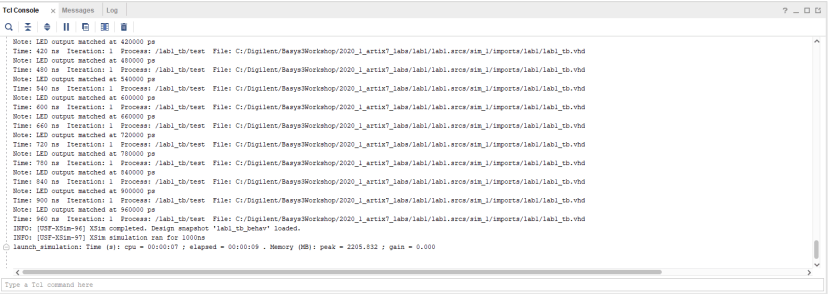

Tcl コンソールを観察し、テストベンチがレポート タスクを使用するときに出力が表示されることを確認します。

図 20. シミュレーションをさらに 500 ns 実行した後の Tcl コンソール出力

File > Close Simulationを選択してシミュレータを閉じます。OKをクリックしてから Noをクリックして、波形を保存せずにシミュレータを閉じます。

デザインの合成 (ステップ 3)

Vivado 合成ツールでデザインを合成し、プロジェクト サマリ出力を解析します。

Flow Navigator ペインの [Synthesis tasks] の下にあるRun Synthesis をクリックします。

合成プロセスは lab1.vhd ファイル (および存在する場合はすべての階層ファイル) で実行されます プロセスが完了すると、3 つのオプションを含む Synthesis Completed ダイアログ ボックスが表示されます。

インプリメンテーション段階に進む前に合成出力を確認するため、[Open Synthesized Design] オプションを選択し、[OK] をクリックします。

ダイアログ ボックスが表示された場合は、[Yes] をクリックしてエラボレートされたデザインを閉じます。

[Project Summary ] タブを選択し、さまざまなウィンドウを理解します。

[プロジェクトの概要] タブが表示されない場合は、Layout > Default Layoutを選択するか、[Project Summary ] アイコンをクリックします。

図 21. プロジェクトの概要ビュー

さまざまなリンクをクリックして、提供される情報と、合成設定を変更できる情報を確認してください。

[Project Summary ] タブの [Table] タブをクリックします。

推定で 3 つの LUT と 16 の IO (8 つの入力と 8 つの出力) が使用されていることに注意してください。

図 22. Basys3 のリソース使用率の見積もりの概要

Flow Navigatorの [Synthesis ] (必要に応じて [Synthesized Design ] を展開) の下で、[Schematic] をクリックして合成済みデザインを回路図ビューで表示します。

図 23. 合成されたデザインの回路図

IBUF と OBUF は、入力と出力がバッファリングされると、自動的にデザインにインスタンス化 (追加) されることに注意してください. 論理ゲートは LUT に実装されます (1 つの入力は LUT1 としてリストされ、2 つの入力は LUT2 としてリストされ、3 つの入力は次のようにリストされます)。 LUT3) RTL 解析出力の 4 つのゲートは、合成出力の 4 つの LUT にマッピングされます。

Windows Explorer を使用して、lab1.runs ディレクトリが lab1 の下に作成されていることを確認します。runs ディレクトリの下に、synth_1 ディレクトリが作成され、合成に関連するいくつかのファイルが保持されます。

図 24. デザイン合成後のディレクトリ構造

設計の実装 (ステップ 4)

Vivado インプリメンテーションのデフォルト (Vivado インプリメンテーション 2020) 設定を使用してデザインをインプリメントし、プロジェクト サマリの出力を解析します。

Flow Navigator ペインの [Implementation tasks] の下にある [Run Implementation ] をクリックします。

インプリメンテーション プロセスは合成済みデザインで実行され、プロセスが完了すると、[Implementation Completed] ダイアログ ボックスに 3 つのオプションが表示されます。

[Open implemented design ] を選択し、[OK] をクリックして、デバイス ビュー タブでインプリメントされたデザインを確認します。

プロンプトが表示されたら [Yes] をクリックして、合成済みデザインを閉じます。

インプリメントされたデザインが開きます。

[Netlist] ペインでネットの 1 つ (例: led_OBUF[1]) を選択し、そのネットが [Device view] タブの X1Y1 クロック領域に表示されていることを確認します (拡大して表示する必要がある場合があります)。

選択されていない場合は、Routing Resources アイコンをクリックして配線リソースを表示します。

図 25. ネットの選択

図 26. Basys3 のインプリメントされたデザインの表示

実装されたデザイン ビューを閉じて、[プロジェクトの概要] タブを選択し (既定のレイアウト ビューに変更する必要がある場合があります)、結果を観察します。

[実装後] タブを選択します。

実際のリソース使用率は 3 つの LUT と 16 の IO であり、このデザインにはタイミング制約が定義されていないことも示しています (デザインが組み合わせであるため)。

図 27. Basys3 の実装結果

Windows Explorer を使用して、impl_1 ディレクトリが lab1.runs ディレクトリの下の synth_1 と同じレベルに作成されていることを確認します。impl_1 ディレクトリには、インプリメンテーション レポート ファイルを含むいくつかのファイルが含まれています。

Vivado で、下部パネルの [Reports] タブを選択し (表示されていない場合は、メニュー バーの [Window] をクリックして [Reports] を選択)、[Place Design] セクションの下の [Utilization Report ] エントリをダブルクリックします。リソース使用率を示すビュー ペイン デザインは組み合わせであるため、レジスタは使用されないことに注意してください。

図 28. 表示可能なレポート

タイミング シミュレーションの実行 (手順 5)

タイミング シミュレーションを実行します。

[Flow Navigator ] ペインの [Simulation tasks] の下にあるRun Simulation > Run Post-Implementation Timing Simulation を選択します。

Vivado シミュレータは、インプリメントされたデザインと lab1_tb を最上位モジュールとして使用して起動されます。

Windows Explorer を使用して、lab1.sim > sim_1 > implディレクトリの下に timing ディレクトリが作成されていることを確認します. timing ディレクトリには、タイミング シミュレーションを実行するために生成されたファイルが含まれています。

Zoom Fit ボタンをクリックして、0 から 200 ns までの波形ウィンドウを表示します。

50 ns (スイッチ入力が 0000000b に設定されている場所) で右クリックし、Markers > Add Marker を選択します。

同様に、右クリックして、LED が変化する約 55.000 ns にマーカーを追加します。

[タグを追加] ボタンをクリックすることもできます ()。 Add Marker ボタンをクリックし、e_led が変化する約 60 ns で左クリックします。

図 29. タイミング シミュレーションの出力

実際の遅延は約 5.000 ns であるのに対し、入力が変更された後 10 ns で期待される led 出力を監視したことに注意してください (テストベンチを参照)。

変更を保存せずにFile > Close Simulation を選択してシミュレータを閉じます。

ビットストリームの生成と機能の検証 (手順 6)

ボードを接続して電源を入れ、ビットストリームを生成し、ハードウェア セッションを開き、FPGA をプログラムします。

Micro-USB ケーブルが JTAG PROG コネクタ (電源コネクタの隣) に接続されていることを確認します。

ボードが USB 電源を使用するように設定されていることを確認します (Basys3 の電源選択ジャンパー JP2 経由)。

図 30. Basys3 のボード接続

ボードの電源を入れます。

[Flow Navigator ] ペインの [Program and Debug tasks] の下にある Generate Bitstream エントリをクリックします。

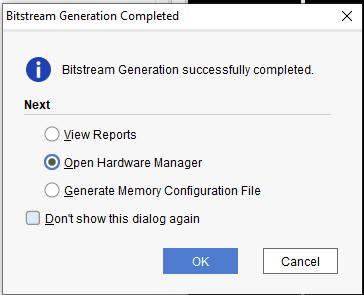

インプリメントされたデザインでビットストリーム生成プロセスが実行され、プロセスが完了すると、[Bitstream Generation Completed] ダイアログ ボックスに 2 つのオプションが表示されます。

図 31. ビットストリームの生成

このプロセスにより、lab1.runs ディレクトリの impl_1 ディレクトリの下に lab1.bit ファイルが生成されます。

[Open Hardware Manager ] オプションを選択し、[OK] をクリックします。

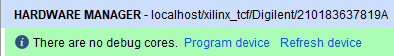

ハードウェア マネージャー ウィンドウが開き、「unconnected」ステータスが表示されます。

[ターゲットを開く] リンクをクリックします。

[ターゲットを開く] リンクをクリックします。

[Auto Connect] をクリックし、Vivado が検出して接続するまで待ちます。

ハードウェア セッションのステータスが Unconnected からサーバー名に変わり、デバイスが強調表示されます。また、ステータスがプログラムされていないことを示していることにも注意してください。

図 33. Basys3 の開いたハードウェア セッション

緑色の情報バーの Program リンクをクリックして、ターゲット FPGA デバイスをプログラムします。

もう 1 つの方法は、デバイスを右クリックして [Program Device…] を選択することです。

図 34. FPGA のプログラムの選択

Program をクリックして FPGA をプログラムします。

デバイスがプログラムされると、DONE ライトが点灯します。スイッチの位置によっては、他の LED が点灯する場合があります。

スイッチを切り替えて LED の出力を観察することにより、機能を確認します (前のロジック ダイアグラムを参照してください)。

問題がなければ、ボードの電源をオフにします。

File > Close Hardware Managerを選択して、ハードウェア セッションを閉じます。

[OK] をクリックしてセッションを閉じます。

File > Exit をクリックして Vivado プログラムを閉じ、[OK] をクリックします。

結論

Vivado ソフトウェア ツールを使用して、完全なデザイン フローを実行できます。 プロジェクトは、提供されたソース ファイル (HDL モデルおよびユーザー制約ファイル) を使用して作成されました。 提供されたテストベンチを使用してビヘイビア シミュレーションを実行し、モデルの機能を検証しました。 次に、モデルを合成して実装し、ビットストリームを生成しました。 タイミング シミュレーションは、同じテストベンチを使用してインプリメントされたデザインで実行されました。 機能は、生成されたビットストリームを使用してハードウェアで検証されました。

Commentaires