Artix-7 FPGA II 的 HDMI I/O 视频处理系统 - 软件

关注文章你觉得这篇文章怎么样? 帮助我们为您提供更好的内容。

Thank you! Your feedback has been received.

There was a problem submitting your feedback, please try again later.

你觉得这篇文章怎么样?

现在我们已完成了硬件设计(请参阅 Artix-7 FPGA I 的 HDMI I/O 视频处理系统 - 硬件),Adam 为系统开发了软件。该软件可以生成视频输出信号并将数据写入 (134-6477) Nexys Video 的 DDR 3 中,这样 VDMA 就可以读取数据并通过 HDMI 输出数据。

步骤 1:定义视频帧

首先要定义视频帧,这些视频帧将被储存在内存中并通过 VDMA 输出。为此,Adam 在内存中定义了三个视频帧,每个视频帧均采用二维阵列:

u8 frameBuf[DISPLAY_NUM_FRAMES][DEMO_MAX_FRAME];

将参数 DISPLAY_NUM_FRAME 设置为 3,DEMO_MAX_FRAME 设置为 1920 * 1080 * 3。如此设置考虑到了最大帧分辨率,并且最后乘 3 以适应每个像素(红色、绿色和蓝色都采用 8 位表示)。

为了访问这些视频帧,Adam 使用一个指针阵列来指向三个帧缓冲区。这样就简化了与视频帧之间的交互。

步骤 2:初始化并配置外围设备

定义视频帧后,下一步就是初始化并配置这款设计的外围设备。它们分别是:

- VDMA – 使用 DMA 将数据从 DDR 3 移动至视频输出链路。

- 动态时钟 IP – 输出像素时钟频率和这个频率的倍数,用于 HDMI 输出。

- 视频时序控制器 0 – 根据分辨率定义输出显示时序。

- 视频时序控制器 1 – 决定所接收的输入的视频时序。在此演示中,控制器从视频源获取输入帧。

为了确保 VDMA 正常运行,Adam 定义了步幅,即 DDR 内存中每行之间的间隔。对于本应用,步幅定义为 3 * 1920,这是一行的最大长度。

在实际应用中,用户可以设置不同的显示分别率,从 640x480 到 1920x1080 不等。无论选取何种分辨率,用户将能够使用可以写入 DDR 3 的软件功能在屏幕上绘制测试图案。如果修改了功能,则 VDMA、视频时序发生器 0 和动态时钟模块也要根据需要进行重新配置。

步骤 3:生成视频输出

下一步是生成视频输出。以下功能可以生成、捕捉以及显示视频。

- 条形测试图案 – 在屏幕上生成几种颜色条

- 混合测试图案 – 在屏幕上生成一个混合颜色测试图案

- 从 HDMI 输入到输出的流传输

- 抓取输入帧并反色

- 抓取输入帧并按比例扩展到当前显示分辨率

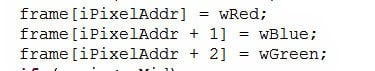

在每个功能中,Adam 都将一个指针传向当前正在输出的帧,以便可以在内存中修改像素值。按照下方设置了红色、蓝色和绿色像素的代码片段操作,即可轻松修改像素值。每个像素颜色值都采用 8 位代码表示。

当 Adam 运行该应用时,可以通过 Output(输出)菜单选择想运行的功能(通过 UART 终端):

通过设置程序以输出颜色条,混合测试输出的效果如下所示:

用户可以通过这种方法生成 Mandelbrot 图案。如需下载项目文件,请前往 Adam 的 Github