RISC-V: An Open Instruction Set Architecture

Follow articleHow do you feel about this article? Help us to provide better content for you.

Thank you! Your feedback has been received.

There was a problem submitting your feedback, please try again later.

What do you think of this article?

An introduction to the open standard processor ISA.

In this article, we take a look at the open standard RISC-V ISA, which has been gathering significant momentum in recent years and is finding applications in everything from the lowest-power IoT devices to supercomputers.

ISA 101

MIPS Add Immediate Instruction. Booyabazooka, CC BY-SA 3.0.

An instruction set architecture (ISA) provides a model for how a computer operates, by specifying things such as the instructions it executes, along with supported data types, registers and addressing modes. Notable examples of which being the Intel 32-bit and 64-bit (IA-32 and x86-64) architectures which dominate the server, desktop and laptop computer markets, and the Arm architecture family which powers the vast majority of mobile, tablet and IoT devices.

Over the years there have been many different ISAs from a variety of vendors, with most having enjoyed some measure of success in at least one market, such as graphics workstations, servers or network equipment. However, the majority of these have ultimately given way to one — or in some cases a small number of — architectures, whose success is typically built on powerful ecosystems; having great silicon technology is one thing, but it takes equally great toolchains and SDKs, and strategic hardware and software partnerships, to succeed in such highly competitive markets.

One of the interesting things about Arm is that they are an intellectual property (IP) vendor, which is to say that they don’t produce physical silicon and rather instead license their IP, such as CPU designs, to semiconductor companies. When they started out their approach was pretty novel, simultaneously saving them the trouble of having to manufacture and sell physical product, while providing customers with essential building blocks which they can combine with their own IP.

However, one thing that nearly all ISAs have in common is that they are proprietary, meaning that one or a small number of vendors are permitted to implement a particular ISA in a CPU design. Even with Arm most licensees just receive drop-in IP blocks, with very few having access to modify the internal workings of a CPU design in order to optimise it for their particular application.

But what if we could have an open ISA?

Free and open

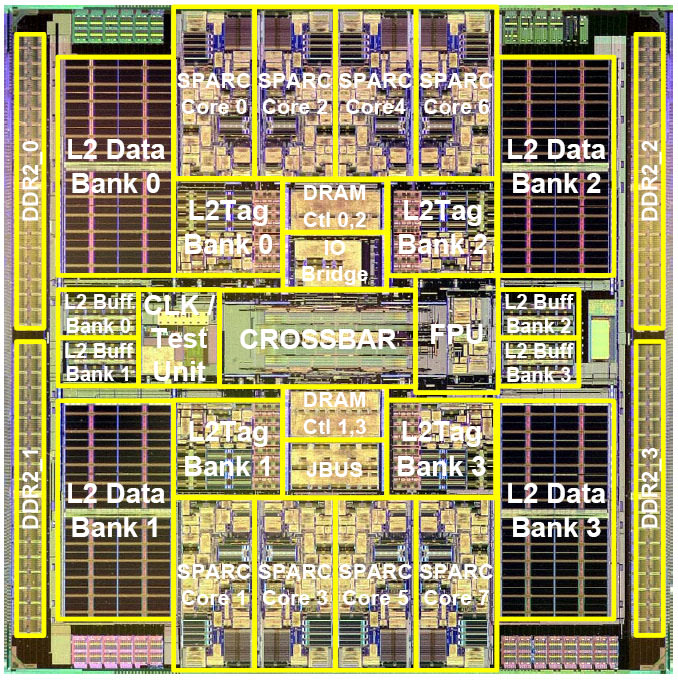

The OpenSPARC T1 processor.

Free and open source principles and practices present similar opportunities in silicon/digital design, as in the development of software — albeit with some obvious differences. Perhaps the most significant opportunities being providing a platform for collaboration, facilitating standardisation, and fostering the development of technology ecosystems. This applies equally to an ISA itself — an abstract specification — and implementations of an ISA that are targeted to FPGA or custom ASIC.

microSPARC IIep.

The first free and open-source digital designs date back to around the late 1990s, with the European Space Agency releasing a GPL/LGPL licensed 32-bit SPARC-V8 based processor design in 1999. Sun Microsystems released the HDL code for the microSPARC IIep — a 32-bit SPARC implementation — also in 1999, albeit under a more restrictive licence and with royalties due in volume production. Sun then notably later went on to release the first OpenSPARC design in 2006, a full 64-bit, 32-thread microprocessor, this time under the free and open source GPL licence.

The OpenRISC project also deserves a notable mention, in providing an open ISA specification which is free for anyone to use, along with implementations and compiler toolchain support.

TechEdSat-1 cubesat (left). Copyright NASA.

However, while open-source SPARC implementations existed, they typically targeted niche applications, such as use in space, education and research. OpenRISC was also mainly to be found in academia and research, though it did find use in a small number of real-world applications, such as a NASA satellite and a digital television system-on-chip (SoC).

Pioneering as they were and with an important place in history, none of these early free and open-source ISA and CPU implementations achieved any measure of widespread adoption.

Enter RISC-V.

RISC-V

The term RISC (reduced instruction set computer) was coined in the early 1980s by David Patterson of the Berkeley RISC project, which carried out groundbreaking research into microprocessor design. This research went to be commercialised by Sun Microsystems as the SPARC architecture and also provided the inspiration for the Arm architecture.

RISC-V started life back in 2010 as the latest generation of RISC-based research out of the University of California, Berkeley. What was initially intended to be a summer project with Professor Krste Asanović and several graduate students, very quickly grew to gather momentum as the ISA was made freely available, other projects started to build on it and demand became apparent.

RISC-V International

The RISC-V Foundation, a non-profit corporation controlled by its members, was established in 2015 to “build an open, collaborative community of software and hardware innovators based on the RISC-V ISA.” Effectively taking over ownership of RISC-V IP and leading its development.

In 2018 the RISC-V Foundation entered into a joint collaboration with the Linux Foundation, and then in 2020 it relocated to Switzerland and incorporated as RISC-V International, citing concerns over U.S. trade regulations and with a desire to be able to freely collaborate globally.

RISC-V International boasts a large membership, which includes companies such as Google, Intel, AMD and IBM. Community Membership is free for individuals, academic and non-profit organisations. While Strategic and Premier membership is available to corporates and can cost anywhere from $2K to $250K a year.

RISC-V IP remains royalty-free, but involvement in the standardisation process and other RISC-V International activities requires membership of the foundation.

Why is it interesting?

Proprietary semiconductor IP licensing typically has a high barrier to entry and it may be that the minimum buy-in for a CPU core design represents an investment of >$1M, with additional royalties due on each device sold. Hence the cost benefit is clear. But this is by no means where the story ends and other benefits include reduced friction in collaborative development projects, plus the opportunity to get involved in the development of the ISA, to name but two.

However, it should be remembered that we are talking about an ISA here and a commercial implementation is likely to come with its own set of terms, which govern things like use, modification and non-disclosure etc. It’s vitally important to separate the ISA spec from a CPU design; these two things are not the same and RISC-V is not a processor!

From a silicon customer perspective RISC-V is exciting similar to how Arm is, in that there is an ecosystem with lots of different vendors, catering to different markets, but implementing the same ISA and hence common development tools, libraries and applications can be used. RISC-V builds on this to give additional freedom to semiconductor companies, while providing a forum and framework for collaboration via RISC-V International. Which should lead to greater diversity in the market and increased pace of innovation.

Products

Early platforms

Yunsup Lee holding RISC V prototype chip. Derrick Coetzee, CC0.

In the early days, there would have been very little physical silicon around, with much more hardware simulation of designs. However, a limited number of prototype chips were fabricated and one from 2013 can be seen pictured above.

In 2016 a crowdfunding campaign was launched by SiFive, a company founded by RISC-V originators, to bring an Arduino-compatible dev kit to market dubbed the HiFive1, which featured their FE310 microcontroller SoC, the RTL design of which was published to GitHub. This was covered in a 2017 DesignSpark article entitled, HiFive1 heralds a new era of silicon freedom.

HiFive Unleashed plus Expansion Board fitted with a GPU and USB3 adapter.

The HiFive1 board was then followed up in 2018 by SiFive’s HiFive Unleashed, which boasted a 4+1 core Linux-capable SoC, 64GB RAM and Gigabit Ethernet. This could be combined with a later expansion board which featured a Microchip PolarFire FPGA, to add PCIe and other interfaces, and which finally enabled a “RISC-V PC” to be created. The only slight issue being that these two boards together cost in the region of $3,000.

Current products

Thankfully, fast forward a few more years and there are now many more microcontroller class RISC-V options, along with far more affordable Linux-capable RISC-V boards. One of the latter being the BeagleV Ahead (268-6957) , from OKdo, a compact RISC-V single board computer (SBC) from BeagleBoard.org, which features a quad-core processor, 4GB RAM, 16GB eMMC and Gigabit Ethernet, amongst numerous other features.

The BeagleV Fire (273-0243) meanwhile features a 4+1 core CPU and 23K logic element FPGA integrated into the same package, courtesy of a Microchip PolarFire SoC. In short offering the same combination of “hard” CPU core performance and FPGA flexibility, as provided by the earlier, much more expensive and far larger, HiFive Unleashed and Expansion Board combination.

We be taking a closer look at both of the BeagleV SBCs in future articles.