冗長性が役に立つとき

この記事を購読こちらの記事について、内容・翻訳・視点・長さなど、皆様のご意見をお送りください。今後の記事製作の参考にしたいと思います。

Thank you! Your feedback has been received.

There was a problem submitting your feedback, please try again later.

こちらの記事の感想をお聞かせください。

回路に二重、三重、さらには四重の冗長性を持たせる「冗長化」は、信頼性を高めるための手法として長年用いられている。冗長設計された最初のシステムが軍事用航空機向けだったのも当然で、当時は冗長化にかかる費用が高額だった。これにより航空機はコンピュータ制御で安全に飛行できるようになり、「フライバイワイヤ」と呼ばれるこの技術によって、航空機の性能は人間のパイロットの能力をはるかに超えるレベルにまで向上した。1960年代のアポロサターンVロケット誘導コンピュータは三重冗長構造で、ロケット発射時の過酷な条件における卓越した信頼性も、この構造のおかげといえるだろう。危険な操作を防止する目的で二重化又は三重化されたハードウェアコンポーネントによる冗長化構成を、Double Modular Redundancy (DMR)又はTriple Modular Redundancy (TMR)と呼ぶ。

センサの冗長性

センサDMRとTMR動作の基本を図1に示す。最新のほとんどのチップセンサはシリアルデジタル出力(例 : UART、SPI、I²Cバス)を備えているため、各センサからのデータを比較する多数決論理デバイスは小型で低電力のマイクロコントローラであることが多いようだ。Modular Redundancyはシステムの信頼性向上のみを目指したセンサフュージョン技術だ。DMRでは重大な障害の検出と、システムの制御されたシャットダウンが可能である。「フェイルセーフ」となる確率を高めているとも言える。TMRは単一の「フォールトトレランス」で、第二のセンサに障害が発生するまで稼働を続行する。どちらの場合においても、各センサからのデータはいかなる形でも結合又は処理されず、単に識別情報を比較するだけで、実際のコンポーネント間で発生した出力のわずかな偏差は許容される。

センサが二重(a)又は三重(b)でも多数決チップはそうではないので、ここが単一障害点(Single Point of Failure : SPF)となる。この問題には冗長多数決論理を追加して対処することもできるが、そのような面倒なことをする前に、まずメーカーが提示したセンサと多数決チップの障害率を比較してみるべきだろう。例えばMicrochipは、ほぼ全てのマイクロコントローラの平均故障時間(Mean-Time-To-Fail: MTTF)統計を公開している。通常の運用でも高い負荷にさらされることの多いセンサは、多数決チップよりもMTTF値がはるかに低くなるはずだ。システム障害率を計算する場合、多数決論理の影響は考慮されないことが多い。

プロセッサ冗長の開発

組み込み制御システムでは、センサ入力データはマイクロコントローラで実行される何らかのソートアルゴリズムによって処理され、アクチュエータとディスプレイを駆動させるための出力データが生成される。このマイクロコントローラは重大なSPFハザードであり、安全性が不可欠な用途では冗長回路を組み込む必要がある。

冗長性を持たせたフライバイワイヤシステムは1960年代のサターンVロケット以降広く採用されており、1988年のエアバスA320を皮切りに、近年は民間航空機でも採用されている。システムの冗長化には非常に多額の追加投資が必要となる。これは物理的ハードウェアへの投資だけでなく、フライトミッションを成功させるための回路/ソフトウェアを設計するためにエンジニアが費やす時間への投資である。

ハードに由来する障害そして一時的な障害の内容と、それぞれの障害率は変化してきている。最近のチップはハードフォールトを起こしにくくなったが、より集積度が高くなったことで、漂遊(宇宙)粒子による一時的な障害が生じやすくなっている。

TMRとフォールトトレランス

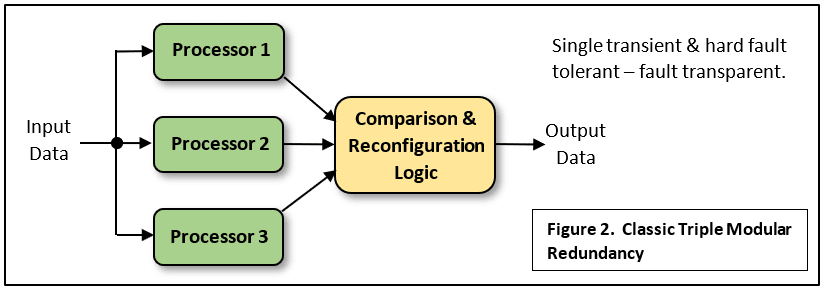

従来のTMRは三重にした同一のプロセッサで同じコードを実行して出力データを論理比較器に通し、3台すべてが同じ結果を生成していることを確認する。同じ結果とは、正常に実行されエラーがないということだ(図2)。もし1台のプロセッサが「ミスをした」場合、その出力は無視することができ、残り2台の一致した出力を正しい結果として通す。これはフォールトマスキングと呼ばれ、中断のない連続した安全動作を実現する。一つの障害によって出力データのフローが中断されないため、システムはフォールトトレラントであるとされる。これはリアルタイム制御の用途には理想的な状態だ。ところがフォールトトレラントなシステムの構築は、必ずしも同一プロセッサの設計の欠陥や各プロセッサで実行している同一プログラムコードのバグに対する防衛策にはならない。

上の図に示すように各プロセッサは同じ入力データを単一の非冗長センサから受信することも可能だが、冗長センサを使用したほうが賢明であることは図1に示す通りだ。このTMRの弱点は、「正しい」データが最終出力に適用されていることを保証するための論理比較が複雑になることと、回路が必要なことである。回路の確認も三重化する必要がある場合もあり、そうなると設計は容易ではない。このテーマについてはこちらの論文に詳しい。

DMRとフォールトリカバリ

フォールトトレラントTMRは複雑であるため、ほとんどの実践的な安全性システムの設計者はフォールトリカバブルDMR構成で折り合いを付ける。エアバスA320航空機のフライトサーフェス(昇降舵、方向舵など)を制御するさまざまなコンピュータは、それぞれ独立して相互にクロスチェックを行なうプロセッサで構成されている。どんな障害が生じても、シャットダウンと別のコンピュータへの機能移転を安全に行なうことができる。こうしたコンピュータのうち5台が巧妙に相互接続された駆動冗長アクチュエータだ。1台の障害では航空機の性能に影響しない。障害台数が増えると性能は低下するが、最後の1台になるまで昇降制御を維持し、冗長方向舵システムと組み合わせることで、機体の安全な操縦と着陸が可能になる。A320航空機の冗長飛行制御システムの詳細については、こちらの技術詳細を参照されたい。

相違性

同一コンピュータと同一ソフトウェアが同一の不正な回答を生成した場合に対処するため、A320では相違性の概念を導入している。5台のうち3台のコンピュータはそれぞれ一対のIntel 80186 16ビットマイクロプロセッサをベースとし、残りの2台はMotorola 68010 16/32bitユニットを搭載している。これらはそれぞれ異なる請負業者が設計・構築・プログラムしていて、唯一共通している点は、冗長外部バスインタフェースとプロトコルだけである。安全性のコストは安くないのだ。

機能安全マイコンと「ロックステップ」

シリコン技術の進化により複数の「コア」を搭載したプロセッサチップが生み出され、デバイスの性能やスループットは大幅に向上した。マルチコアデバイスは冗長性を備える代わりに、複数の異なるプログラムを真に並行処理できる機能を備えている。今日において、自律的に動作する機械というのも現実味を帯びてきている。例えば無人運転の自動車や製造工場全体の無人化などだ。実用に際しては、当然ながら機能安全性が非常に大きな問題となる。幸い、自律型製品の設計及び安全性認証を監督する規格が設定されている。産業用装置の機能安全に関するIEC 61508、自動車用途向けのISO 26262といった規格がある。チップメーカーは新しいデバイスクラスで対応している。それが機能安全マイクロコントローラです。こうした新しいデバイスのほとんどはDMR原則に基づいているが、さらに一工夫加えられている。2つのプロセッサコアは同じプログラムを実行するが、1つ又は複数のクロックサイクルは互いに同調しない(図3)。出力はエラー検出の目的で再調整される。

2つのプロセッサ間の固定ディレイは、両方のコアに同時に影響する一時的な障害を確実に検出します。これをコアが「ロックステップ」で動作していると言う。さらなる冗長性を含めることで、フリップされたメモリビット(誤り訂正符号, ECCロジック)及び通信チャネル上のフリップされたビット(巡回冗長符号, CRC)に対応します。次に組み込み自己テスト(Built-In Self-Test: BIST)ロジックがあり、コアデータの不一致が検出されるたびに起動します。ハードフォールトがなければ、BISTはフルリセットによって一時的な障害を回復することができる。それだけではない。チップは、両方のコアに共通で生じる故障が最小限となるよう配置されています。Texas InstrumentsのHercules TMS570シリーズのチップレイアウトを図3に示す。2つのコアを互いに対して90°となる配置し、最少間隙を100μmに配置します。

ロックステップ機能安全マイクロコントローラには、他にもInfineonのAURIX、STMicroのSPC5、NXPのS32S24などがあります。

人工知能と冗長システム

プロセッサの冗長性は、安全性が重要なシステムにAIを採用する際に課題となる点の克服にも役立つだろう。この課題とは、物体認識のためのディープラーニングでは「教える」画像を非常に慎重に選ばないと想定外のバイアスが生じるということだ。これが無人自動車の視覚システムにとって致命的な故障の原因になりうることは想像に難くない。解決案としては、自動車で稼働する各「推論エンジン」を異なる画像セットから作成された異なるデータセットによって実行させるシステムに、三重化の冗長構成を実装することだ。これで、少なくとも2つのプロセッサが同時に正しい処理を行なう確率は高くなるはずである。

フルサークル

サターンVロケットのコンピュータのような完全なフォールトトレランスが必要であれば、欧州宇宙機関が開発したフォールトトレラントコアのLEONシリーズを利用することができる。これは、サービスを中断せずとも宇宙粒子によるシングルイベントアプセットのほとんどに対応することができる。

冗長性は命を救う(はず)

ボーイング737のエチオピア航空EA302便墜落事故は、設計のわずかな変更でも大惨事につながる恐れがあることを世界に示した。現代の航空会社はどこも広範な冗長安全性システムを備えており、例えばコックピット内にはパイロットを「二重化」している。二重化フライトセンサは二重化した飛行制御コンピュータにデータを送り、そのデータはコックピットの両サイドに表示される。コンピュータ間でクロスチェックを行うことで有効なセンサデータが確認され、最終バックアップとして人間のパイロットが身を乗り出してお互いの計測値を比較します。新型737 Maxの問題は、離陸時にフルエンジンパワーが印加されると失速状態の可能性を示す追加警告を発するMCASというシステムが追加されたことだった。オートバイでウィリーをする時のように、航空機は機首が上がってしまいがちです。737 Maxにこの警告システムが必要だった理由は、機体の高い位置かつ前方寄りに搭載された大型のエンジンが飛行に与える負の影響を抑制するためだった。

新しい警告システムは、2つある迎角(Angle-of-Attack: AOA)センサのうち1つだけを監視していた。旧式の機械的な「風見鶏」形式は信頼性が低いことを考えれば、これは重大な故障だ。事故の起きた302便では、AOAが突然変化したことを、新しいMCASシステムは危険な機首のピッチアップ(機首上げ)と解釈してしまった。もしもう一つ冗長AOAが接続されていれば、AOA不一致警告が鳴動し、パイロットがMCASを無効にできただろう。実際、適切に設計された冗長システムであれば、ピトー管センサと加速度計からの情報もサニティチェックとして使用できたはずだ。冗長性がなかったため、不正なセンサによってMCASは失速状態が迫っていると判断し、パイロットの操縦ハンドルを右前方に押した。あらゆる失速状態はパイロットのヒューマンエラーによって生じるとの仮定の元にシステムは設計されていたので、MCASによって強制的に動かされた操縦ハンドルは、パイロットの力で引き戻すことができなかった。もっと機械に冗長性をもたせていれば、この事故は防ぐことができたかもしれなかったのだ。人間のパイロットを実質上の「冗長」にしてしまったことが、大惨事の引き金となったのである。