Wie viel schneller läuft ein Algorithmus in einer FPGA-Struktur als in einem Prozessor ab?

Artikel folgenWie finden Sie diesen Artikel? Helfen Sie uns, bessere Inhalte für Sie bereitzustellen.

Vielen Dank! Ihr Feedback ist eingegangen.

There was a problem submitting your feedback, please try again later.

Was denken Sie über diesen Artikel?

Ein programmierbares Logikgatter (Field Programmable Gate Array, FPGA) ist ein Schaltkreis mit logischen Schaltern, die Hardware-seitig dazu programmiert sind, eine nutzerdefinierte Aufgabe zu bearbeiten. FPGAs haben den Vorteil, dass viele Berechnungen oder Anweisungen parallel ausgeführt werden. So wird die Rechengeschwindigkeit im Vergleich zu prozessorbasierten Plattformen signifikant gesteigert. Aufgrund eingebauter Hochgeschwindigkeitsressourcen wie DSP und schnellem Speicher werden FPGAs derzeit auch zur Beschleunigung von Algorithmen verwendet.

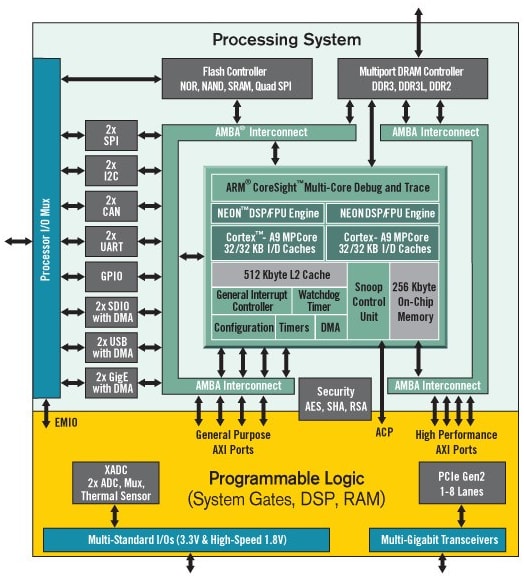

Das vorliegende Projekt vergleicht die Geschwindigkeit eines Pi-Schätzwert-Algorithmus, der einmal in einem FPGA und einmal auf einem Prozessor läuft. Dazu wird ein Pi-Schätzwert-Algorithmus mit der Monte-Carlo-Methode auf einem Prozessor und einem FPGA-Gatter auf Basis eines Digilent Cora Z7 Zynq-7000 mit Einkern- und Zweikernoptionen für ARM/FPGA-SoC-Entwicklung ausgeführt. Die Architektur mit Xilinx Zynq-7000 integriert einen Einkern- oder Zweikernprozessor des Typs ARM Cortex-A9 mit 667MHz in eine FPGA-Struktur der Xilinx-7-Baureihe.

Zynq-APSoC-Architektur

Die Produktvarianten von Cora Z7 heißen Cora Z7-10 (184-0484) und Cora Z7-07S (184-0456) . Der einzige Unterschied zwischen dem Cora Z7-10 und dem Cora Z7-07S ist die Leistungsfähigkeit der Zynq-Komponente. Das Cora Z7 hat viele Hardware-Schnittstellen, von 1-Gbps-Ethernet-PHY zu Analog-zu-Digital-Wandlern und allgemeinen Eingang/Ausgang-Steckern und ist deshalb die ideale Plattform, um darauf viele verschiedene integrierte Anwendungen zu programmieren.

ProduktvarianteCora Z7-10Cora Z7-07S

| Zynq-Bauteil | XC7Z010-1CLG400C | XC7Z007S-1CLG400C |

|---|---|---|

| ARM-Prozessorkerne | 2 | 1 |

| 1 MSPS On-chip ADC | Yes | Yes |

| Lookup-Tabellen (LUTs) | 17,600 | 14,400 |

| Flip-Flops | 35,200 | 28,800 |

| DSP Slices | 80 | 66 |

| Block-RAM | 270 KB | 225 KB |

| Clock Management Tiles | 2 | 2 |

Cora-Z7-Zynq-7000-Plattform

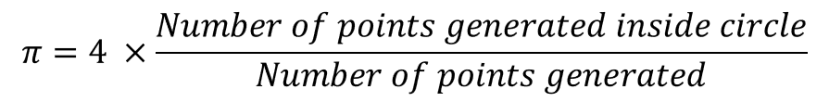

Wie man Pi mit der Monte-Carlo-Methode schätzt

Viele Webseiten erklären die Funktion der Monte-Carlo-Methode zur Schätzung von Pi. Schauen Sie sich dazu diese Website an. Bei der Methode wird zunächst eine große Zahl zufälliger Punkte erzeugt. Dann wird geprüft, wie viele davon innerhalb des Kreises liegen, den das Einheitsquadrat umschließt. Die Fläche des Quadrats ist 1 und die Fläche des Kreises ist Pi/4, da der Radius 0,5 beträgt. Bei einer großen Anzahl zufälliger Punkte (x,y) gilt:

Um den Algorithmus zu implementieren, erzeugt man einfach einen zufälligen Punkt (x, y) und prüft dann, ob die Entfernung des Punktes zum Ursprung (x,y) weniger oder gleich 1 ist (x2 + y2 <= 1). Falls ja, so erhöht man die Anzahl der Punkte, die innerhalb des Kreises liegen.

Ausführen des Algorithmus auf einem ARM-Prozessor unter Linux

DasTutorialerklärt Ihnen, wie Sie Linux auf dem Cora-Z7-ARM-Prozessor starten. Dann können Sie die Programmiersprache GO verwenden, um Pi mit der Monte-Carlo-Methode zu schätzen. Sie benötigen dazu Ubuntu 16.04.3,Xilinx Viavdo 2017.4,PetalinuxsowieGolang. Golang können Sie mittels apt-get installieren. Die anderen Werkzeuge müssen Sie über die Xilinx-Webseite herunterladen. Zum Starten von Linux benötigen Sie Petalinux.

Die folgende Tabelle zeigt Ihnen, wie lang die Cora-Z7-Varianten jeweils zur Berechnung von 100.000 Monte-Carlo-Datenpunkten benötigte.

Ausführen des Algorithmus in einem FPGA-Gitter

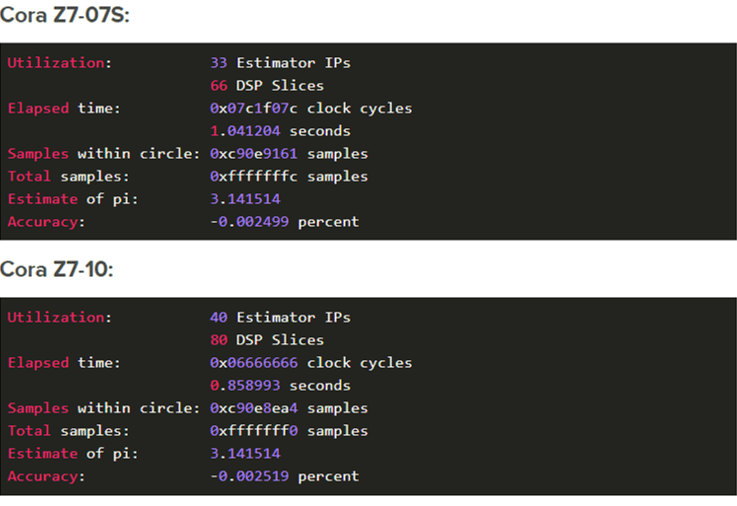

DiesesTutorialzeigt Ihnen, wie Sie den Algorithmus in der FPGS-Logik erstellen können. Die FPGA-Struktur enthält Elemente namens DSP-Slices. DSP steht für Digitale Signalverarbeitung. Bei der Monte-Carlo-Methode müssen Sie zwei Multiplikationen ausführen (x*x and y*y). Solange das Ergebnis jeder Multiplikation weniger als 48 Bits breit ist, benötigen Sie nur zwei der DSP-Slices von Cora pro Code-Instanz, die die Monte-Carlo-Simulation berechnet. Zufällige Werte werden mittels eines linear rückgekoppelten Schieberegisters (LFSR) erzeugt, wobei der Grundwert von der Steuereinheit zur Verfügung gestellt wird. Das gesamte System läuft auf 125 MHz. Beim Testlauf wurden so viele Instanzen ausgeführt, wie in einen 32-Bit-Integer passten.

Die Ergebnisse der beiden Cora-Varianten sehen Sie hier:

FPGA vs. Prozessor

Die langsamere Variante der beiden Cora-Z7-Maschinen konnte in ca. einer Sekunde so viele Datenpunkte erzeugen, wie in einen vollen 32-Bit-Integer passten. Die schnellere Variante erzeugte unter Linux in 1,8 Sekunden nur 100.000.000 Datenpunkte. Mit anderen Worten ist die Hardware-beschleunigte Version des Algorithmus 77-mal schneller als die langsamere Variante. Das FPGA-Gitter kann 9 Monte-Carlo-Datenwerte pro Taktzyklus erzeugen (wobei ein Taktzyklus 8 Nanosekunden dauert).