FPGAボード「Artix-7」で HDMIビデオ信号を処理 - (2)ソフトウェア編

この記事を購読こちらの記事について、内容・翻訳・視点・長さなど、皆様のご意見をお送りください。今後の記事製作の参考にしたいと思います。

Thank you! Your feedback has been received.

There was a problem submitting your feedback, please try again later.

こちらの記事の感想をお聞かせください。

この記事はFPGAボードでHDMIの信号処理に挑戦するAdam氏の記事の日本語版で、 ハードウェア編(refer to HDMI I/O Video-Processing System on the Artix-7 FPGA I - Hardware) の続きになります。 ここでは、生成したビデオ信号を、Nexys Videoボード (134-6477) のDDR 3にデータを書き込むため、HDMIのVDMAを介してこのデータを読み取り、出力するソフトウェアを開発していきます。

手順1: ビデオフレームの定義

最初に、ビデオフレームを定義します。ビデオフレームはメモリに保存され、VDMAで出力されます。このために、Adamはメモリ内に3つのフレームを定義しました。各フレームは次のような2次元配列になっています。

u8 frameBuf[DISPLAY_NUM_FRAMES][DEMO_MAX_FRAME];

DISPLAY_NUM_FRAMEには3、DEMO_MAX_FRAMEには1920 x 1080 x 3が指定されています。ここではフレームの最大解像度を考慮に入れており、最後の乗算(x 3)は、各ピクセルに対応しています(赤、緑、青に対してそれぞれ8ビット)

これらのフレームにアクセスするために、Adamは3フレームの各バッファについてポインターの配列を使用し、フレームとのやりとりを容易にしました。

手順2: ペリフェラルの初期化と設定

フレームを定義した後は、次のように設計内のペリフェラルを初期化して設定します。

- • VDMA – DMA を使用してDDR 3から出力用ビデオチェーンにデータを移動します。

- • ダイナミッククロッキングIP – HDMI出力用にピクセルクロック周波数及びこの周波数の倍数を出力します。

- • ビデオタイミングコントローラー0 – 解像度に基づいて、出力ディスプレイタイミングを定義します。

- • ビデオタイミングコントローラー1 – 受信する入力のビデオタイミングを決定します。このデモでは、このコントローラーが送信元から入力フレームを取得します。

VDMAを正しく機能させるために、AdamはDDRメモリ内の各行を区切るストライドを定義しました。このアプリケーションでは、行の最長の長さである3 x 1920をストライドとして指定します。

アプリケーションについては、640 x 480から1920 x 1080まで、ユーザーは異なるディスプレイ解像度を設定できます。どの解像度が指定されたとしても、ユーザーはDDR 3にデータを書き出すソフトウェアの機能を使って、画面上にテストパターンを描くことができます。もし機能が変更された場合は、VDMA、ビデオタイミングジェネレーター0、ダイナミッククロッキングモジュールも再設定する必要があります。

手順3: ビデオ出力の生成

次に、ビデオ出力を生成します。次の処理を通して、ビデオの生成、キャプチャ及び表示を行います。

- バーテストパターン – 画面上で複数のカラーバーを生成

- 混合テストパターン – 画面上で混合カラーのテストパターンを生成

- HDMI入力からHDMI出力へのストリーミング

- 入力フレームの取得と色の反転

- 入力フレームの取得と現在のディスプレイ解像度に基づくスケーリング

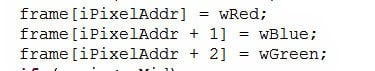

各処理内で、Adamは現在出力中のフレームにポインターを渡し、メモリ内でピクセルの値を変更できるようにしました。赤、青、緑のピクセルを指定する次のコードスニペットでわかるように、この処理は簡単にできます。各ピクセルカラーには、8ビットが割り当てられています。

アプリケーションの実行時、AdamはUART端末を介し、メニュー出力によって次のどの処理を実行するかを指定することができます。

カラーバーと混合テストを出力するようにプログラムを設定すると、次のような出力結果が得られました。

ユーザーはこの方法を使ってマンデルブロパターンを生成することができます。なお、プロジェクトファイルは、Adamの次のサイトからダウンロードできます。Github