FPGAとASICの世界: パート1

この記事を購読こちらの記事について、内容・翻訳・視点・長さなど、皆様のご意見をお送りください。今後の記事製作の参考にしたいと思います。

Thank you! Your feedback has been received.

There was a problem submitting your feedback, please try again later.

こちらの記事の感想をお聞かせください。

写真提供: Microsoft Research

この2部構成記事のパート1では、多くの基板設計のチップ数を減らしたプログラマブルハードウェアの原点を探っていく。パート2では、現在、高速・高信頼性用途において、FPGAとASICがどのようにマイクロプロセッサとDSPを置き換えつつあるかについて解説する。

初期のデジタルロジック

プログラムを実行する初の半導体ベースのコンピュータが製作されたのは、1953年のマサチューセッツ大学だった。92個の点接触型トランジスタと550個のダイオードが使われたが、なんとか実現できた平均命令実行速度は約33命令/秒しかなかった。それでも消費電力が低く、物理的に小型化されているため、先行の熱電子管バルブ(「チューブ」)ベースのコンピュータに比べれば、少なくとも大きな進歩だった。これが開発競争の初期の開始点となったのだ

すべてのデジタルコンピュータは、今でさえ、相互接続された論理ゲートで構成されている。負論理形のNANDとNORがよく使われている。この形式だと必要なトランジスタ段の数が最少になり、伝播遅延と消費電力が少なくできるためだ。これらの論理関数はビルディングブロックとして非常に便利で、初の商用集積回路設計もこれらを採用していた。

1960年代後期から1970年代初期のコンピュータには、TLLやCMOSゲートチップを満載した基板が何枚も入っていた。IC技術が向上するにつれ、カウンタやシフトレジスタなどの「特殊関数」を搭載した新しいチップが登場し、基板の枚数が減り、コンピュータの小型化に寄与した。大規模集積(LSI)によって初のRAMチップが作られ、続いてマイクロプロセッサが製造された。しかし、シングルチッププロセッサとメモリチップだけの構成でさえ、純粋なシングルボードコンピュータを作ることは非常に困難だった。まだ特定の設計に固有の「グルーロジック」が数多く必要で、それらは基本的なゲートコンピュータから作る必要があったからだ。

ゲートアレイ

チップメーカーはプログラマブルアレイロジック(PAL)及びUncommitted Logic Array (ULA)と呼ばれるカスタマイズ可能なデバイスの製造を開始した。PALには、プロダクトタームと呼ばれる固定のAND/ORゲートのグループが含まれ、各グループ内でゲートはヒューズリンクで相互に接続されている。その後、紫外線で消去可能なリンクメモリを使用し、再構成が可能になった。さらに、EEPROMベースのチップが登場し、そのまま再プログラムできるようになった。新しいデバイスには、フリップフロップ・乗算器・RAMブロックが含まれ、汎用性が上がった。

超大規模集積(VLSI)の登場により、これらのプログラマブルデバイスは非常に複雑になり、電源投入時にEPROM又はフラッシュチップからSRAMに読み出された情報で内部コンフィギュレーションメモリを形成するようになった。これがFPGAだ。

メーカーは、開発者が個々のトランジスタ/ダイオードレベルで独自のチップを設計することができるソフトウェアツールセットを提供した。つまり、カスタマイズ設計と同等のものを、重複や不要な素子なしに、速度と消費電力に最適化して作成できる。反面、設計者は、共通クロック、電力、接地接続を含む内部素子を考慮して、基板レイアウトのようなデバイスの「トラック」レイアウトを生成しなければならなかった。

ユーザーはシリコン上の各素子の厳密な位置の図と、すべての相互接続になる金属膜のマスクをメーカーに提出する。ULAに高密度素子を含めることはできなかったため、作業全体はむしろ基板の設計によく似ていた。ULAは、実際に、現在、特定用途向け集積回路(ASIC)と呼ばれている完全カスタマイズが可能なデバイスの初期の形態だった。ASICは、顧客固有の設計で製造されるため、誤りがあると非常に高くつく。そのため、FPGAなどを用いて設計が完全に実証されない限り、ASICで製作されたものを手にすることはない。初期のPentiumマイクロプロセッサには、FDIVバグと呼ばれる設計ミスがあり、Intelに何億ドルもの損失を与えた。

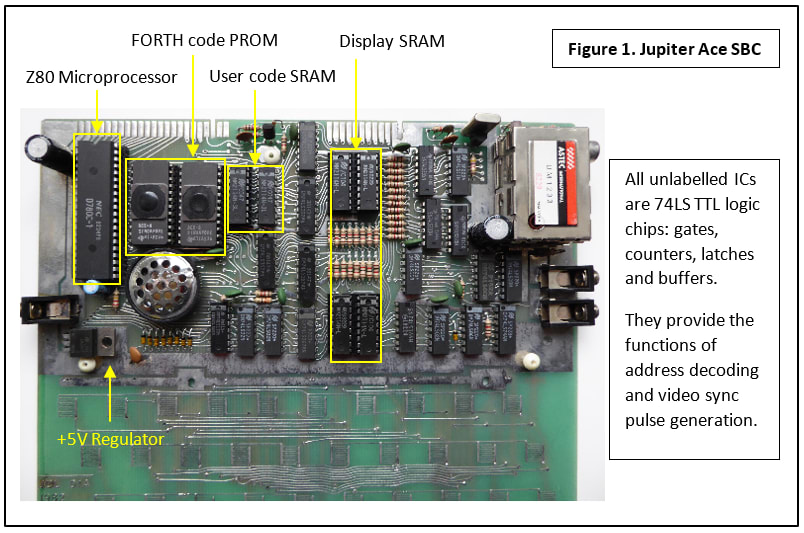

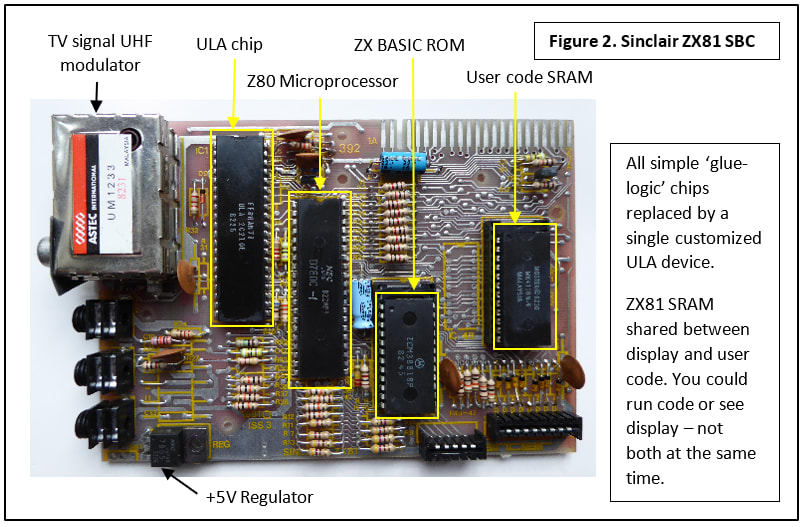

プログラマブルロジックによる省スペースの例

下の写真は1980年代のシングルボードコンピュータの基板2枚だ。1枚にはシンプルな「グルーロジック」チップが多数搭載されており(図1)、もう1枚はシングルULAデバイスだ(図2)。多くの人は、少なくともClive Sinclairの画期的なZX81を耳にすることになるだろう。Forthプログラミング言語を使用するJupiter Aceはそれほど有名ではない。メンブレンキーボードの土台の部分を除いても、Jupiter Aceには沢山のチップのために広い面積が必要なことは明らかだ。ZX81の回路もよく似ているが、SSI/MSI (Small-/Medium-Scale IC)はすべてシングルULAチップに統合されている。興味深いことに、ZX81はAceより1年早く発売されている。このことは、どんな設計も売上の影響を逃れられないことを示している。Aceの売上ではULAのコストを正当化できなかった。

FPGAはPALやULAの時代から大きく飛躍した。オンボード機能モジュールはますます複雑になり、シングルチップに詰め込まれる数も増え続けた。そのプログラムにはVHDLやVerilogといった高水準言語を使用す。これらは最近まで非常に高価で、メーカーの予算をはるかに超えていた。しかし状況は一転している。パート2では、人工知能などの用途で、どのようにプロセッサやDSPがFPGAに置き換えられているかを見ていく。

しかし、シンプルなグルーロジックの代わりはどうだろう?基本的な論理関数だけの小さくて安価なデバイスが必要なのであれば、安心してほしい。PALは、シンプルプログラマブルロジックデバイス(SPLD)という新しい名称でまだ生き残っている。FPGAとASICは、Complex Programmable Logic Devices (CPLD)と呼ばれるようになった。Raspberry Piのような最新のシングルボードコンピュータが、もはやグルーロジックを必要としなくなったように思われる理由は何だろうか?パート2で探っていく。

行き詰ってしまった場合は、是非Twitterで私の投稿をフォローしてほしい。新しいエレクトロニクスと関連技術、ロボットについて目星をつけた投稿のリツイート、宇宙探査などの興味深い記事にリンクしている。