Arty Z7-20, Xilinx ZYNQ 入門

この記事を購読こちらの記事について、内容・翻訳・視点・長さなど、皆様のご意見をお送りください。今後の記事製作の参考にしたいと思います。

Thank you! Your feedback has been received.

There was a problem submitting your feedback, please try again later.

こちらの記事の感想をお聞かせください。

前回の記事で、XilinxZynq All Programmable SoC, Xilinx Vivado Design Suite 及び Xilinx Software Development Kit (SDK)に対しての基本的な知識を得ることができた。実装にはDigilent ZYBO (134-6462) を使用した。

この記事では、Xilinx SDSoCの使い方を学んでいく。Xilinx SDSoCは、組込みアプリケーションをC/C++/OpenCLで開発するための最新環境だ。Digilent Arty Z7-20 (136-8071) などのFPGAデバイス上で動作するプログラムを開発できる。ハードウェアでの実行には、Xilinx All Programmable SoC Zynq-7000 Z70-20 Development Platform を使用する。以下のチュートリアルはAdam Taylor氏によって書かれたものである。

Xilinx SDSoCによる ソフトウェア&ハードウェア デザイン

Zynq が幅広い用途で採用される理由は、 ARMコアとプログラマブルロジックが効率よく連携できる点にある。このおかげで、システムにおいてARM側に適した処理(例えば高度な命令の実行など)と、プログラマブルロジックに適した処理(画像処理など)を効率的に分担することができる。

もちろん、今までのZynq開発の流れはVivado と SDKでの開発を分離していた。しかし、この方法ではプログラマブルロジック(PL)とプロセッシングシステム(PS)の間で関数を共有することが難しいため、最適なシステムパフォーマンスが得られなかった。

そこで、SDSoCの出番である。SDSoCはコンパイラを最適化しているシステムであり、ソフトウェアによるPSとPLの両方の開発を可能にする。一般的に、SDSoCによる開発は次のような流れで行われる。

- 高級言語によってアプリケーションを開発する。

- サポートされているパフォーマンス評価機能を使い、性能の向上を妨げている処理を特定する。

- 特定したボトルネックに対してプログラマブルロジックを使うことで速度を向上させる。

- パフォーマンスを再び確認し、もし必要ならば他の部分のデザインも改善する。

HLS(High-Level Synthesis)及びフレームワークの連結によって、PSとPLの間で関数を容易に共有することができるようになっている。

SDSoCの基初期設定

プログラマブルロジックの最適なパフォーマンスを得るためには、HLSが何を最適化させるのか決定するなど、高速化させる関数に含まれる最適化プラグマを決める必要がある。

CやC++,OpenCLなどの高級言語を使って、Zynqベースの開発をしてみよう。SDSoCを快適に使うため、ハードウェア及びソフトウェア環境を決める初期設定が必要となる。Arty Z7 (136-8071) の場合、このGitHubのリンクからSDSoCの設定ファイルを入手できる。これによってArty系の開発をSDSoCを用いて行うことができる。

SDSoC入門

このチュートリアルでは、SDSoCを使って行列の積の計算サンプルを高速化させる方法を学ぶ。

Step 1: 次に示す手順で、SDSoCの新しいプロジェクトを作る。

File -> New -> Xilinx SDx Project

実行すると、以下のようなダイアログが表示される。この画面では、プラットフォームの確認、OSの選択、アプリケーションのサンプルの選択を行う。

新しいプロジェクトを作成

ハードウェアとしてArt7 Z7-20を選択

Operating System (OS)とCPUの選択

アプリケーションのサンプルの選択

Step 2: github からArty Z7-20の環境をダウンロードするため、Add Custom Platform をクリックしよう。これでプラットフォームリストの中に希望するプラットフォームが追加され、プロジェクトに追加できるようになった。

Step 3: 以下に示す手順でプロジェクトを完成させると、SDx Project SettingページがSDSoCに表示される。これを使うことで、関数をPSとPLの間で共有できるようにする。Add HW Function をクリックし、PLに移動させたい関数を選択することで共有できるようになる。

PSで実行されている関数をPLに移動させて高速化させたい場合、以下のルールに従わなければならない。

- OSの機能を呼び出す関数を含んではいけない

- 関数はすべての機能を含んでいなければならない

- Cの文法が一定のルールに従う必要がある

- 構文は明確である必要がある

Project Setting画面では、PLとPSの通信を行うデータモーションネットワークのクロックを設定することができる。

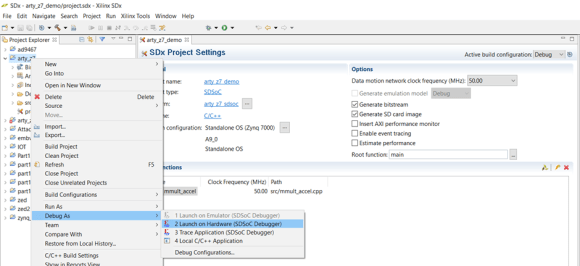

SDSoC Project Settings画面(SDSoCの主な設定はここからできる)

高速化できる関数の表示

Step 4: プログラムをビルドすると、SDカード上のプログラムを実行するのに必要なbinファイルが生成される。また、必要であればZynqにアプリケーションのサンプルをダウンロードするだけでなく、デバッガを使うこともできる。これには時間がかかることがあるので、高速化させる関数を選ぶときは、サポートされている機能を使ってどの程度高速化されるのか予測しよう。Project Settingタブにあるestimate performance optionをクリックすることで設定できる。

実行すると、以下に示すような結果が表示される。

予測結果

estimate performance optionのチェックを外してビルドすれば、デバッガを使いながらサンプルを実行することができる。

デバッガは、プロジェクトを右クリックし、Debug As -> Launch on Hardware (SDSoC Debugger)によって起動できる。

デバッガの起動

デバッガを起動すると、Arty 27にアプリケーションがダウンロードされる。SDSoCのターミナルをArty 27のUARTと接続することで、実行したサンプルの結果が表示される。

SDSoCアプリケーションの開発を行う際には、SDSoCでサポートされているライブラリに注目しよう。

アプリケーションをさらに高速にするため、SDSoCはいくつかのHLSライブラリを備えている。例えば以下のようなものがある。

- reVision Stack – 3つの要素からなる開発ソフトを提供する。これにより、OpenCVやCaffe(ニューラルネットワークの開発に用いられるオープンソースのフレームワーク)を使用することができる。 reVision は OpenCVの高速化を可能にする。

- Math Library – 統合可能な計算用ライブラリを提供する。

- IP Library – FFTやFIR, Shift Register LUT などの機能を実行するためのIPライブラリを提供する。

- Linear Algebra Library –線形代数学用の関数を提供する。

- Arbitrary Precision Data Types Library – signed,unsigned integerを使った任意長データなど2のべき乗でない数を提供する。このライブラリを用いることでFPGAのリソースをより効率的に使用することができる。

まとめ

このサンプルを通じて、関数をPSとPL間でやり取りすることが簡単であることが分かったと思う。PLに処理を任せることで、パフォーマンスを大きく向上させることができる。