Accélérez vos applications openCL avec la plateforme Digilent Genesys ZU-3EG Zynq Ultrascale+ MPSoC

Suivez l'articleQue pensez-vous de cet article ? Aidez-nous à vous fournir un meilleur contenu.

Merci! Vos commentaires ont été reçus.

There was a problem submitting your feedback, please try again later.

Que pensez-vous de cet article ?

Le déterminisme, la réactivité et les performances sont des critères qui dictent l’architecture de la plupart des applications embarquées de pointe dans un grand nombre de domaines tels que la conduite autonome, la robotique et les systèmes de vision avancés.

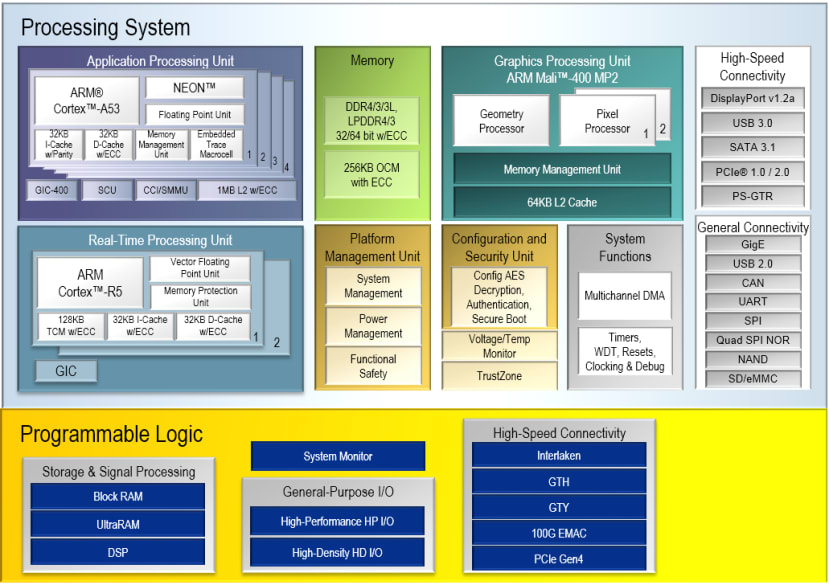

Les appareils Xilinx Zynq® UltraScale+™ EG MPSoC (176-0795) combinent un système multicœur et multiprocesseur aux performances élevées basé sur une architecture ARM® avec une logique programmable de classe ASIC. Le système de traitement (PS) est équipé de processeurs en temps réel ARM® Cortex®-A53 64 bits à quatre cœurs et Cortex-R5F 32 bits à deux cœurs, ainsi que d’une unité de traitement graphique Mali™-400 MP2. La logique programmable de classe ASIC très flexible est intégrée à l’architecture Xilinx UltraScale. Elle communique avec le système de traitement via 6000 interconnexions. L’architecture offre aux ingénieurs la possibilité d’implémenter des solutions qui leur permettent d’atteindre leurs objectifs en termes de déterminisme, de réactivité et de performances.

Schéma fonctionnel d’appareil Zynq Ultrascale+ MPSoC EG (source : https://www.xilinx.com/content/dam/xilinx/imgs/products/zynq/zynq-eg-block.PNG)

L’association du système de traitement et de la logique programmable permet d’implémenter des algorithmes et des fonctions à l’aide de la technologie d’implémentation la plus adaptée. Les communications réseau peuvent être implémentées dans le système de traitement tandis que l’accélération apportée par le réseau neuronal permet de tirer profit de la nature hautement parallèle de la logique programmable. Avec les systèmes hétérogènes sur puce Xilinx, les ingénieurs et développeurs peuvent aussi accélérer les algorithmes depuis le processeur en utilisant des langages de programmation de haut niveau.

La dernière plateforme de développement logiciel unifiée Xilinx Vitis permet le développement de logiciels embarqués et d’applications accélérées sur les plateformes hétérogènes Xilinx telles que telles que les FPGA, les SoC et les Versal ACAP. Elle offre un modèle de programmation unifié qui vous donne la possibilité d’accélérer les applications de traitement Edge, Cloud et Hybrid. Tirez le meilleur parti de l’intégration avec des frameworks de haut niveau, développez en C, C++, OpenCL ou Python à l’aide de librairies accélérées ou utilisez des accélérateurs basés sur les RTL et des API d’exécution de bas niveau pour un meilleur contrôle de l’exécution du programme — Choisissez le niveau d’abstraction requis par les ingénieurs ou les développeurs. La plateforme offre ainsi aux développeurs les performances de la logique programmable sans langage de description de matériel (HDL).

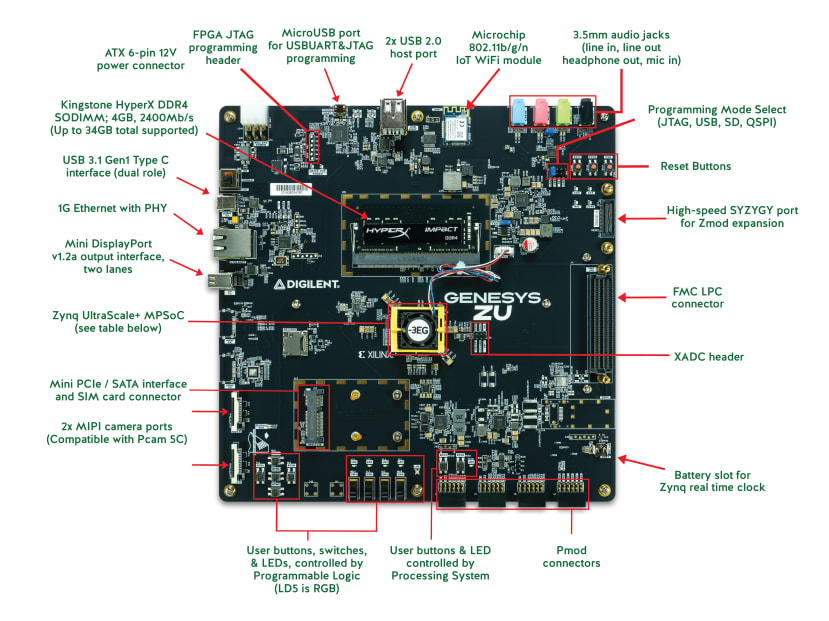

La Digilent Genesys ZU-3EG (200-3904) est une carte autonome Zynq Ultrascale+ Zynq MPSoC conçue avec des spécifications, fonctionnalités multimédia et interfaces de connectivité réseau optimisées. Elle comporte une librairie de documentation de qualité qui vous permet de vous lancer rapidement dans le développement d’applications d’IA, de recherche, d’aérospatial/défense, de cloud computing et de vision embarquée. La carte offre une excellente combinaison de périphériques intégrés tels qu’une DDR4 que vous pouvez facilement mettre à jour, un port Mini PCIe, des ports microSD, une multi-caméra et l’USB 3.0, et une expansion à la vitesse élevée. Adam Taylor, expert en conception embarquée, est à l’origine de la plateforme d’accélération Vitis pour la plateforme Digilent Genesys ZU-3EG Zynq Ultrascale+ MPSoC et montre différents éléments nécessaires pour créer une plateforme d’accélération.

Plateforme Genesys ZU-3EG Zynq Ultrascale+ MPSoC

Applications OpenCL

OpenCL est un framework open-source conçu pour les systèmes hétérogènes. Son hôte est généralement un système x86, tandis que son noyau peut être de différents types tels que CPU, GPU, FPGA ou ASIC. L’objectif d’OpenCL est de permettre la portabilité entre plateformes sans modifier le code source. Ainsi, l’application hôte est souvent codée en C ou C++ en combinaison avec l’interface de programmation d’application (API) d’OpenCL. Les noyaux sont développés en OpenCL C, un dérivé de l’ISO C99 comportant les limitations et changements nécessaires. Par exemple, les en-têtes standards tels que stdlib.h, stdio.h ne sont pas autorisés, tandis que les types scalaires ont une taille définie contrairement au C/C++, où leur taille dépend du compilateur et de l’architecture. Cela permet aux développeurs d’utiliser OpenCl avec des compilateurs standards tels que GCC, alors que le noyau utilise des compilateurs personnalisés fournis par le fabricant du noyau.

Le module OpenCL peut être utilisé pour le développement du système de traitement (hôte) et de la logique programmable (noyau) sur le Xilinx Zynq Ultrascale+ MPSoC. Une telle approche est supportée par l’outil de développement logiciel unifié de Xilinx Vitis.

Outils Xilinx pour le flux d’accélération Vitis OpenCL sur la Digilent Genesys ZU-3EG

- Xilinx Vivado – Créez une plateforme de configuration matérielle de base qui met à disposition du compilateur Vitis les ressources nécessaires

- Xilinx PetaLinux – Créez le système d’exploitation Petalinux qui contient l’API d’OpenCL et supporte l’allocation de mémoire contiguë ainsi que les pilotes d’accès direct à la mémoire. PetaLinux est également utilisé pour créer le SYS Root qui assure le support de la plateforme d’accélération Vitis.

- Xilinx Vitis – Créez la plateforme d’accélération Vitis et l’application accélérée ainsi générée.

Qu’inclut la plateforme d’accélération Vitis ?

Plateforme matérielle de base

Une plateforme Vivado de base contient les interfaces et éléments de traitement et met les ressources nécessaires à disposition du compilateur de Vitis. Pour utiliser ce design matériel de base avec des outils en aval, le XSA qui définit la configuration matérielle doit être exporté afin qu’un fichier binaire puisse être créé. Le compilateur Vitis peut ensuite générer les fichiers binaires nécessaires à l’application.

Cette plateforme doit au minimum définir

- La configuration du processeur – La configuration du système de traitement, les horloges, la DDR disponible et sa configuration, et la configuration des entrées/sorties multiplex pour les périphériques d’interfaçage PS.

- Les horloges – Plusieurs horloges différentes utilisables avec le compilateur Vitis sont fournies par un assistant de réglage de l’heure. Deux horloges à 150 MHz et 300 MHz sont proposées.

- Interrupteurs – Un interrupteur est fourni au système de traitement par un contrôleur d’interrupteur AXI. Les interrupteurs connectés au contrôleur d’interrupteur AXI sont ensuite mis à disposition du compilateur Vitis. Cette plateforme comporte huit interrupteurs.

- Blocs de réinitialisation du processeur – Un bloc de réinitialisation du processeur doit être fourni au compilateur Vitis pour chacune des horloges disponibles.

- Interface PS / PL – Au moins un Maître PS AXI et un Esclave PS AXI doivent être définis. Cela permet de configurer et contrôler le noyau d’accélération créé, ainsi que de réaliser des transferts DMA à haute vitesse du PL au PS si nécessaire. Il y a un master AXI et trois interfaces esclaves AXI.

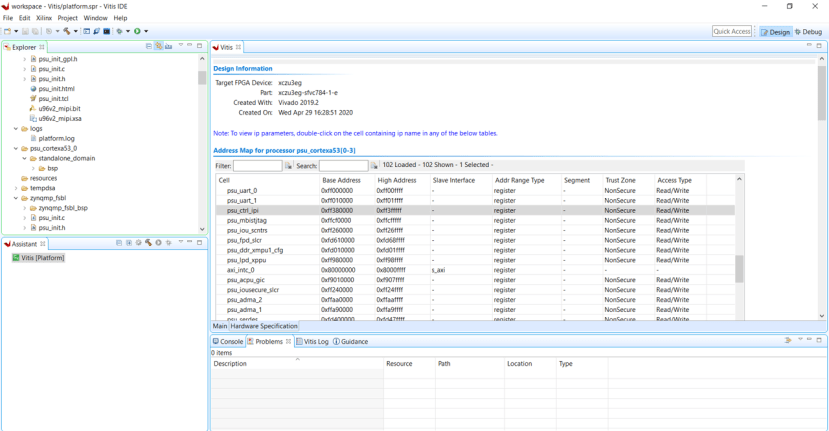

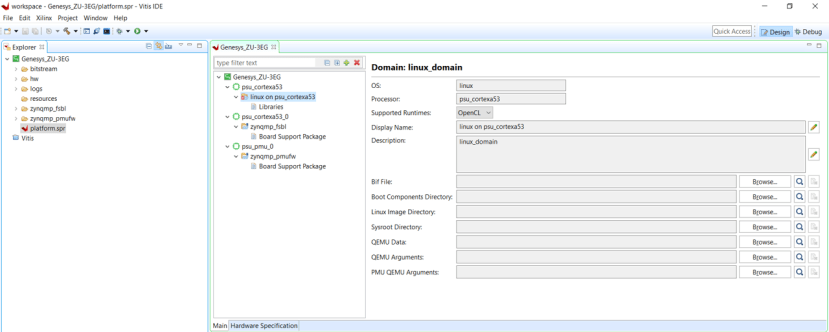

Plateforme matérielle de la Genesys ZU-3EG dans Vitis

Images Linux

Le XSA exporté peut être utilisé pour créer et configurer un nouveau projet PetaLinux destiné à la Genesys ZU-3EG. Une fois que le projet ainsi que le SYS Root ont été créés et configurés, une plateforme Vitis a besoin des éléments suivants créés par PetaLinux

- elf – Chargeur de la première étape du démarrage

- ub – L’image du noyau elle-même

- elf – Le micrologiciel de l’unité de gestion de la plateforme

- elf – Le micrologiciel d’ARM TrustZone

- U-Boot.elf – Chargeur de la deuxième de l’initialisation qui s’exécute dans l’image du noyau

- À partir de ces éléments disponibles à la fin de la séquence de compilation, nous pouvons commencer à travailler à la création d’une plateforme d’accélération avec Vitis.

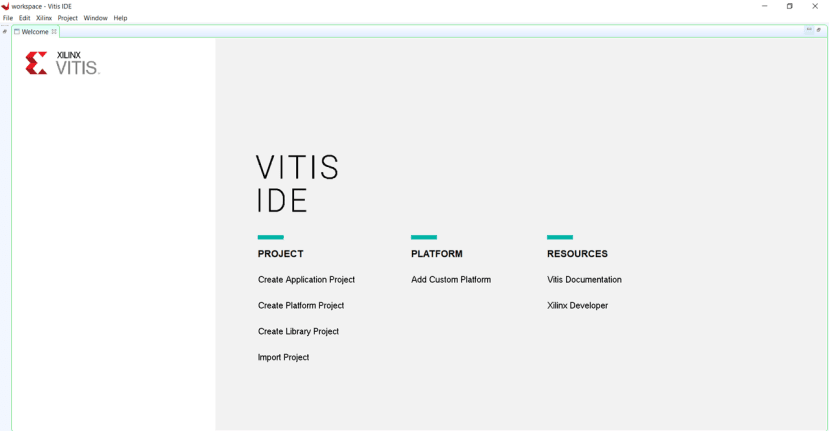

Créer le premier projet d’accélération avec Vitis

- Créer la plateforme Vitis

Vitis fournit un assistant à plusieurs étapes pour aider les utilisateurs à créer une plateforme. L’assistant est listé sur la page d’accueil de Vitis. Sélectionnez « Créer un projet de plateforme » pour créer la plateforme.

Les éléments matériels et logiciels sont requis au sein du matériel d’une plateforme d’accélération. L’élément matériel est défini par le XSA précédemment exporté depuis Vivado. Les éléments logiciels sont produits durant la compilation de PetaLinux et sont identifiables dans l’assistant. Une fois cette étape terminée, la plateforme peut être utilisée dans un nouveau projet d’accélération.

Assistant de l’IDE Xilinx Vitis

Définition des éléments logiciels de Xilinx Vitis

2. Créer le premier projet d’accélération Vitis

Pour terminer le test de la plateforme d’accélération, la méthode la plus simple est de compiler l’une des applications d’exemple existantes. Créez une nouvelle application système destinée à la plateforme Genesys ZU-3EG. Cette plateforme devrait supporter le développement embarqué et l’accélération.

En naviguant dans l’assistant de création d’un nouveau projet d’application, vous pourrez créer l’application d’exemple d’addition de vecteurs. Cet exemple contiendra un noyau OpenCL accéléré dans la logique programmable.

Dans le noyau, plusieurs pragmas sont utilisés pour contrôler le déroulage de boucle et l’interfaçage afin d’optimiser les performances de l’implémentation en logique programmable. Ce bloc accéléré doit être connectable avec les interfaces AXI mises à disposition sur la plateforme Vivado.

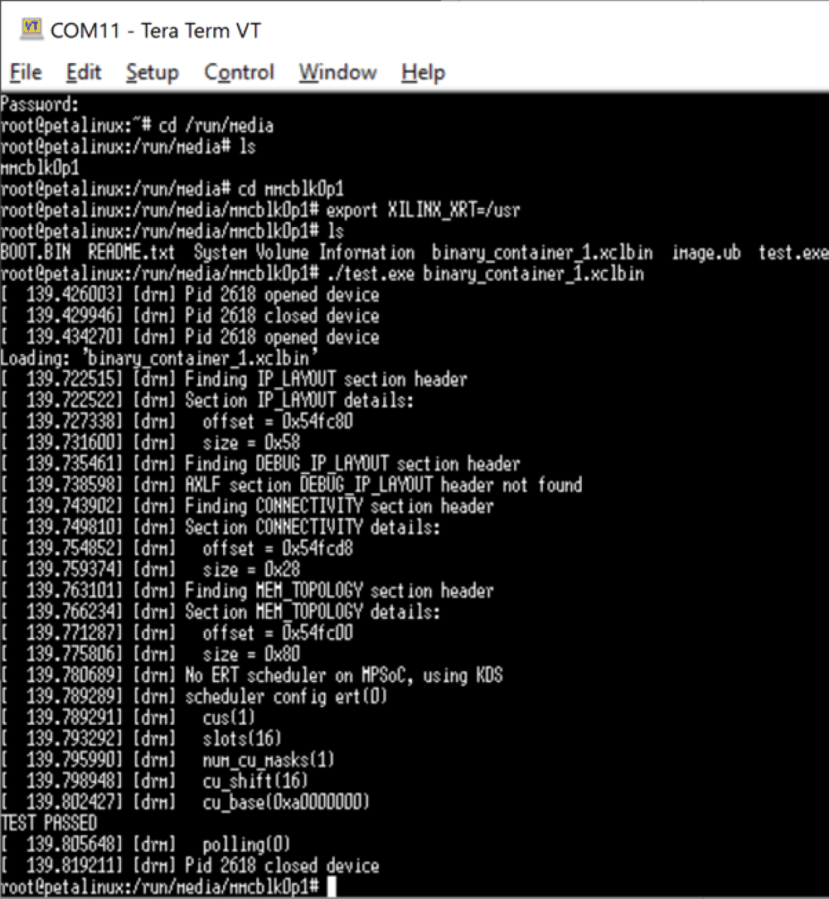

La compilation du projet prendra un certain temps. Une fois que le projet est terminé, Vitis vous fournira tous les fichiers à copier sur la carte SD. Une fois que la carte SD est insérée dans la Genesys ZU-3EG, l’application peut être testée via la ligne de commande. Exécuter l’application affiche les informations relatives au chargement du noyau dans la logique programmable et aux étapes associées à l’exécution du programme.

Application de test