Red Pitayaを解剖!

この記事を購読こちらの記事について、内容・翻訳・視点・長さなど、皆様のご意見をお送りください。今後の記事製作の参考にしたいと思います。

Thank you! Your feedback has been received.

There was a problem submitting your feedback, please try again later.

こちらの記事の感想をお聞かせください。

こちらの記事をもとに作成しています。

プログラマブルなテスト・計測プラットフォーム「Red Pitaya」の秘密を探る

Red Pitaya (901-0302) には多様なアプリケーションを入手できる"Bazzar"というオンラインポータルサイトがあります。それはスマートフォンとアプリストアのような関係になっており、一般的な計測機とは異なる点と言えます。この記事では、それがどのように実現されているのか、特に柔軟性のあるハードウェアとオープンソースソフトウェアスタックに関して探っていきたいと思います。

ハードウェア

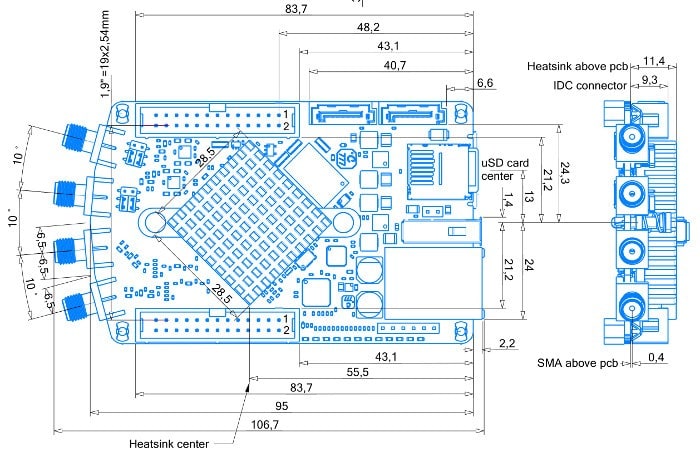

ハードウェアプラットフォームの中心には、 デュアルコアARMプロセッサ、FPGA、各種ペリフェラルの3つを一つのパッケージに統合したXilinx製「Zynq SoC」が使われています。ARMとペリフェラルは、あわせてプロセッシング・システム(PS)とよばれ、OSやアプリケーションを動作させるPCのような役割を担っています。システムとしては、RAMが512MB搭載され、ストレージとしては32GBまでのマイクロSDカードが利用でき、通信用にギガビットのイーサネットとデバッグ用のUARTインタフェースをもっています。

FPGAには28,000のプログラマブル論理セルに、RAMとDSPが搭載されています。これらは、メインのADコンバータとDAコンバータのインターフェースやハードウェア処理の実装(集中演算機能向け)、カスタムインターフェース・拡張などに利用されています。

Red Pitayaの高速デジタル変換器は125MS/s・14bitの分解能をもった2つのアナログ入力と2つのアナログ出力を提供します。これらは、FPGAとAXIバスを介してプロセッシング・システムへと接続されています。上の図は、 Zynqの外部端子とPS、アプリケーションモジュールへの接続を記述したトップモジュールのRTLファイルのヘッダにあるASCIIアートで書かれたブロックダイアグラムです。

アナログ拡張コネクタには、それぞれ100kS/sで12bitの分解能をもつ、4つの低速アナログ入力と4つの低速アナログ出力があります。ボードの反対側にある類似のコネクタには、デジタルの拡張にFPGAの16のGPIOが接続されています。

2つのSATAコネクタを通じてボードをデイジーチェーン接続可能で、それぞれ2つの作動対線によって最大500Mbpsのデータ転送をサポートしています。SATAのコネクタは、広く利用されていることからケーブルが低価格であり、性能がよいために利用しているもので、SATAのドライブは使用できないので注意してください。

ソフトウェア

ボードでは、BusyBoxによるカスタムRAMディスクを利用し、Xilinxから提供されているLinux 3.9.0が動作しています。電源投入時、次のファイルがSDカードから読み込まれます。

-

boot.bin: 第1段階のブートローダ、FPGAイメージとU-Boot

-

uImage: Linuxカーネル

-

devicetree.dtb: Linuxデバイスツリー(ペリフェラル等の記述)

-

uramdisk.image.gz: rootファイルシステムを含む、初期RAMディスク

ブートされると、低メモリ消費で高性能のWebサーバnginxが起動されます。これは、HTMLとJavaScriptベースのWebアプリケーションをクライアントのブラウザに提供するために使われます。WebサーバはサーバサイドのLinuxアプリケーションやコントローラ、FPGAとそれをインタフェースとして、ADコンバータ、DAコンバータに接続されています。つまり、それぞれのアプリケーションは、Webユーザインターフェース、サーバサイドのコントローラ、FPGAモジュールの3つのコンポーネントから構成されます。

SSHを通してリモートに実行可能なコマンドラインツールがあり、テストやデバッグに有効なGNU OctaveやMatlabなどといったソフトウェアが使用できます。これらはLinuxのバイナリであり、ソフトウェアアーキテクチャでは、ADコンバータとDAコンバータのインターフェースであるFPGAと接続されたコントローラと並んで存在します。そのようなツールが1つ、信号生成と取得用に現在提供されています。

開発者向け

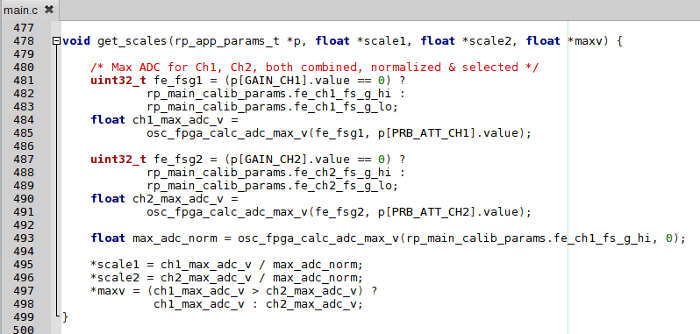

オシロスコープアプリケーションコントローラのmain.cファイルの一部

RedPitaya GitHubリポジトリには次のソースコードがあります

-

FPGAデザインソース(/FPGA/)

-

Linuxカーネル、U-boot、rootファイルシステム (/OS/)

-

Nginx、コントローラモジュールローダなど (/Bazaar/)

-

Webアプリケーション (/Applications/)

-

コマンドラインツール (/Test/)

OSのサブディレクトリには、完全なLinuxとU-bootのソースは含まれていません。これらは他からクローンされていたり、かわりにプラットフォーム依存のパッチやconfigなどのみが含まれていたりします。

FPGAビットストリームはXilinxのISE WebPack(無料)かVivado Designソフトウェアを使うことで生成することができます。GUIを使うよりも、コマンドラインツールやスクリプトを実行するMakefileベースのビルドシステムを使い、それらの生成を行います。

WEBアプリケーションのHTMLやJavaScriptコードは、テキストエディタで簡単に編集できます。コントローラやコマンドラインツールは、C言語で記述されているので、PC上でARMクロスコンパイラをビルドできます。大体のLinuxディストリビューションでは、ARMツールチェーンをインストールするのにほんの数コマンドを実行するだけです。

Bazaarを通して配布するため、アプリケーションはユニークなアプリケーションIDが付与されます。そのID名で一つのディレクトリに入れられ、ZIPとしてパッケージされています。加えて、Webアプリとコントローラには、アイコンとその名前、ディスクリプション、バージョンなどの情報が含まれたJSONファイルを用意する必要があります。

現時点では、すべてのアプリケーションは、ブートに組み込まれた同じFPGAビットストリームが利用されています。しかし、新たなもしくは修正したFPGAベースのDSPを実装するアプリケーションの一部としてカスタムなビットストリームを配布することも可能です。また、たとえば、他の計測機器を制御したり、GPIOを通して外部ペリフェラルのインタフェースをしたりすることができます。

詳しくは、Developer Guideをご覧ください。

まとめ

プログラマブルロジックを備えるZynq SoCは、ハードウェアによる信号処理とともにデジタルコンバータを統合したカスタムIOを実装するのに適したソリューションです。Zynq SoCは柔軟に再構成可能ですが、アプリケーション開発でこれらを使いこなすには、少しばかり学習が必要になります。しかし、たくさんの新しいアプリは、今あるFPGAの設計をそのまま、もしくは少しだけ修正して利用することができるでしょう。

LinuxやWebテクノロジに基づいて、Red Pitayaをカスタマイズしさまざまな用途に拡張することができるでしょう。たとえば、ローカルもしくはリモートのデータベースをロギングしたり、SNMPを通してアラームを送信したり、パブリックなAPIを通してオンラインサービスと統合したりすることも考えられます。

提供されているソースコードは、ASCIIアートのダイアグラムやたくさんのコメントとともに、よく構造化されており、加えてWiki上にドキュメントが提供されています。このように、プラットフォームに新たに触れる開発者が開発しやすいようになっています。